FPGA 处理视频SDRAM带宽计算

多路视频通过 FPGA 写入或读出 SDRAM 需要多少带宽?多路视频进出SDRAM时该怎么计算SDRAM的带宽?FPGA 处理视频时,像素占用内存的位宽一般按整数位宽(8、16、32 便于图像分割计算地址),24位真彩在SDRAM中一个像素占 32位内存。

假设内存数据总线宽度32位,24位真彩视频一个像素占32位,

考虑多路读写SDRAM仲裁效率,动态RAM刷新等,我们按80%的效率来计算(多路仲裁读写SDRAM效率能做到大于80%就不错了)。

一路1920x1080@24P60视频写进或者读出SDRAM内存的速率为 1920x1080x60/0.8 = 156MHz@32。

一路1920x1080@24P30视频写进或者读出SDRAM内存的速率为 1920x1080x30/0.8 = 78MHz@32。

例如:XILINX FPGA ARTIX-7 外接 800MHz@32bit DDR3 SDRAM

800/156 = 5 能支持 5路 1920x1080@24P60视频进出内存。

800/78 = 10能支持10路 1920x1080@24P30视频进出内存。

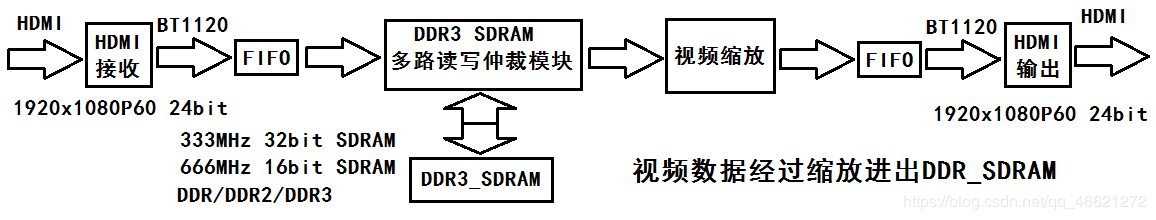

1080P60 单画面拼接器,将一路视频的一部分(比如田字四拼接屏,画面四分之一,一个角)放大到全屏。

按2x2 田字四拼接屏举例,见下图,一路视频进内存(也可以裁剪出画面的四分之一进内存),出内存->视频只读出这需要显示的四分之一数据,进行放大到1080P全屏。

一路视频进内存后再出内存,需要计算2次带宽。这个方案需要占用

1920x1080x60x2/0.8 = 312MHz@32 带宽。

我们在做这个产品硬件设计时需要选大于 333MHZ@32bit 或 666MHZ@16bit 内存方案 (DDR/DDR2/DDR3/DDR4)

在一些需要缩放的产品中,比如输入640x480@24P75转换为1920x1080@24P60输出(视频缩放、变帧率)也可以采用该方案。

举例阐述:FPGA 四路2K60输入,1路2K60输出。四画面分割器SDRAM的带宽计算(文档还没写完,近期会及时更新)

举例阐述:FPGA 四路2K60输入,1路4K30输出。四画面分割器SDRAM的带宽计算(文档还没写完,近期会及时更新)

举例阐述:FPGA 四路2K60输入,1路2K60输出。四画面拼接单元SDRAM的带宽计算(文档还没写完,近期会及时更新)

以上数据在 XILINX FPGA ARTIX-7 XC7A35TFGG484I-2、XC7A100TFGG484I-2、XC7A200TFGG484I-2 这些芯片上做过验证。

有用过其他不同型号 FPGA 、不同速率 SDRAM 做过类似产品的,恳请将您的经验和数据分享给大家。

作者:qq_708907433