FPGA学习之Cyclone器件资源结构知识介绍

因为下周将进行RAM核调用及系统设计学习,这周结束我就先参考Cyclone IV器件手册,来学习FPGA器件(本文学习器件为Cyclone IV E系列器件)一些基础知识,进而熟悉器件资源定义以及设计所注意的使用细节。

https://blog.csdn.net/sinat_41653350/article/details/103955348

中也提到了FPGA器件的硬件资源,但个人所提的只是比较片面和基础的,对初学者来说,是比较不怎么友好的能够理解的。

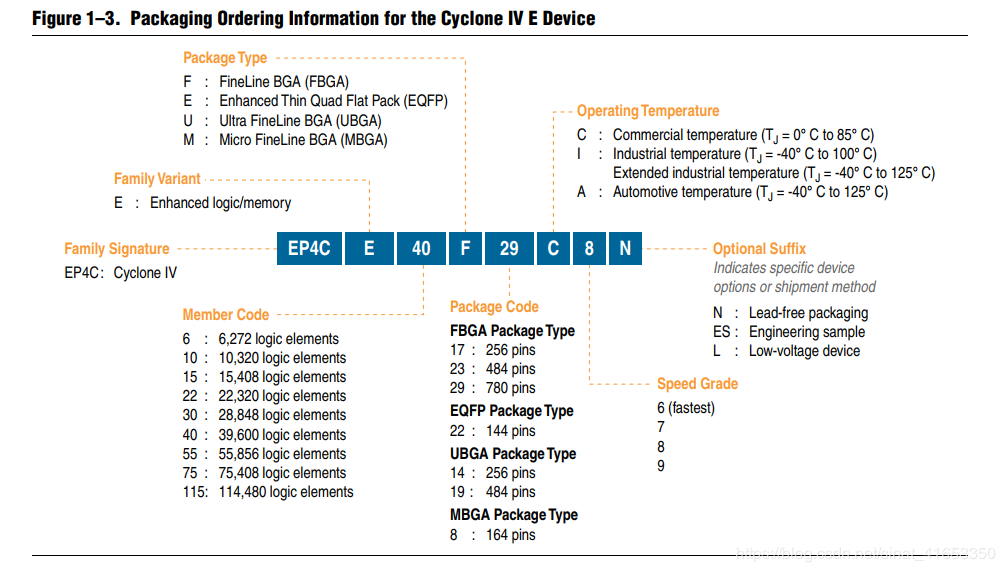

总体命名组成:器件系列 + 器件类型(是否含有高速串行收发器) + LE逻辑单元数量 + 封装类型 + 高速串行收发器的数量(没有则不写) + 引脚数目 + 器件正常使用的温度范围 + 器件的速度等级 + 后缀

器件资源占比

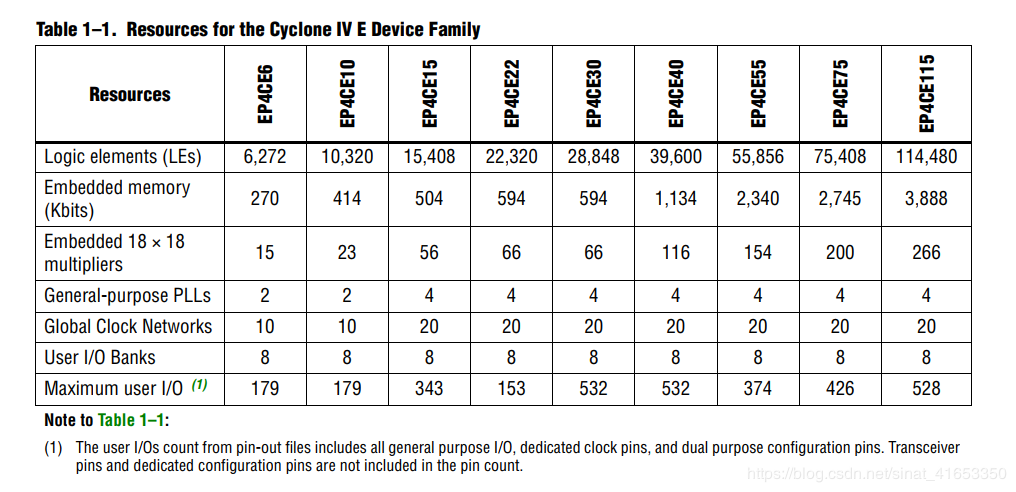

上面表格来自于Cyclone IV E器件手册,上面描述了该系列器件所占资源及结构:

按表格依次排序为:

1.逻辑单元(LE)

2.嵌入式存储器(Kbits)

3.嵌入式18x18乘法器

4.通用PLL

5.全局时钟网络

6.用户I/O块

7.最大用户I/O块:注释:列表6中的用户 I/O 管脚包括所有的通用 I/O 管脚、专用时钟管脚以及两用配置管脚。收发器管脚和专用配置管脚不包括在这一管脚列表中。

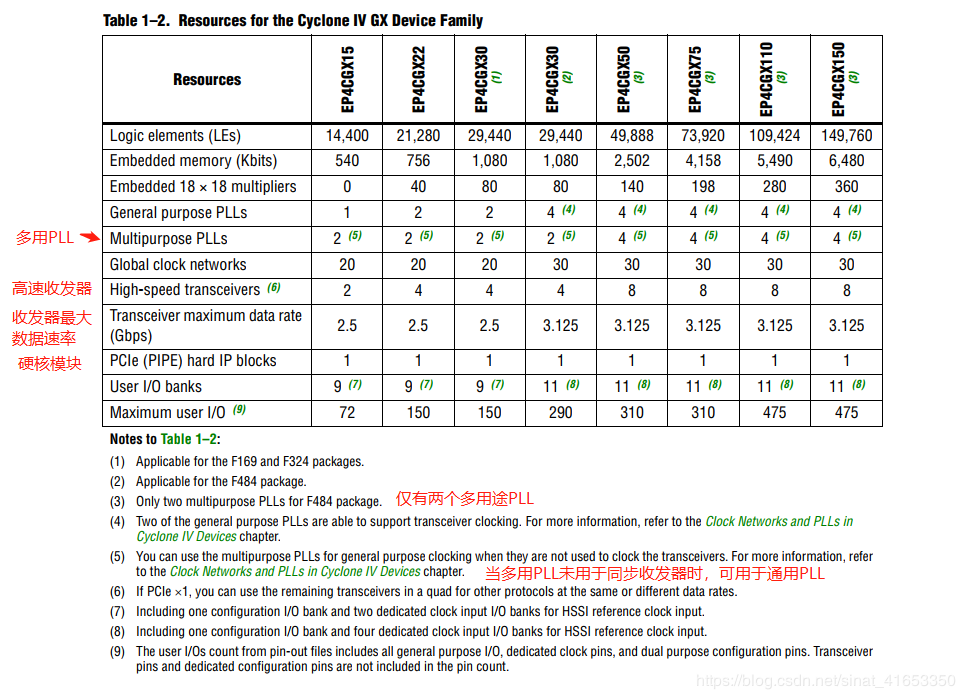

下表是Cyclone IV GX系列器件占用资源,用作对比

我们要入门FPGA设计以及后续的时序分析学习,那么必须了解FPGA器件内部的工作方式。

为什么说FPGA是一门硬件描述语言,因为FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件,PCB是通过导线将具有相关电气特性的信号连接起来,FPGA也需要通过内部连线将相关的逻辑节点导通,因此说FPGA设计实质上也就是电路设计。

首先介绍一下这几种资源所代表的的含义与电路是咋样的吧?

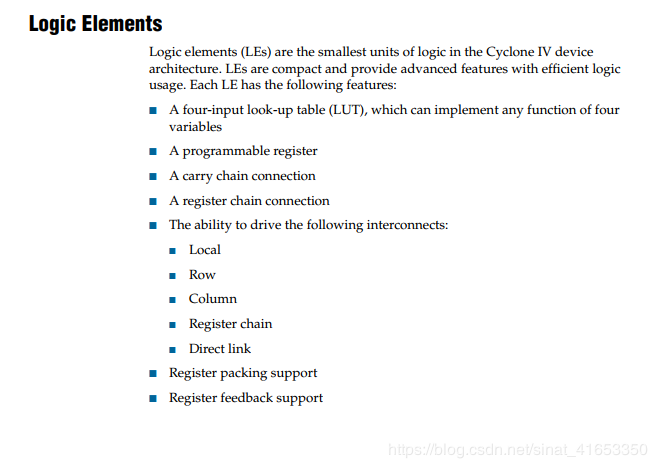

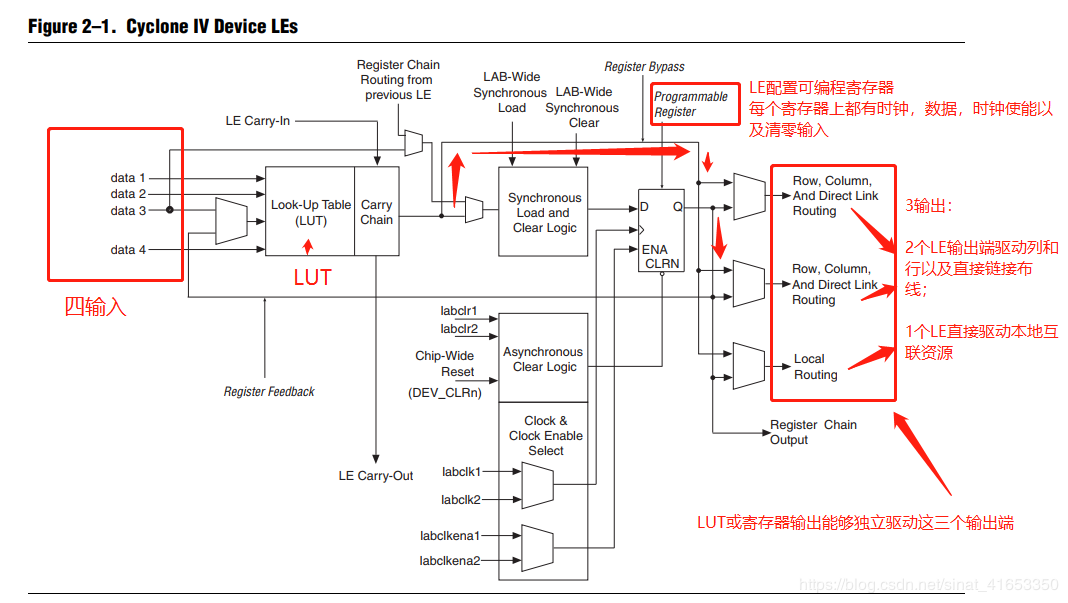

1.逻辑单元(LE)逻辑单元(LE)在Cyclone IV器件中是最小的逻辑单元,逻辑单元特性如下图所示:

上图中提出逻辑单元的核心架构其实是一个四口输入的查找表(LUT)构成的逻辑单元,可以实现四种变量的任何功能。(上图特性第一条)。下图是逻辑单元LE具体构成结构。

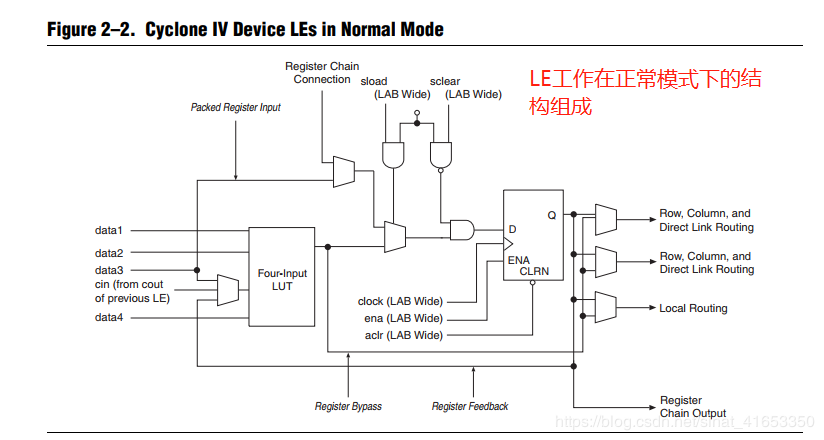

逻辑单元在器件中有两种工作模式,分别是正常模式和算法模式,Quartus II软件自动为普通功能选择适用的模式,例如计数器,加法器,减法器和算术功能,与参数化功能如参数化模块库 (LPM) 功能一起。下图是逻辑单元LE工作在正常模式下的组成结构,与上图介绍特点基本一致。

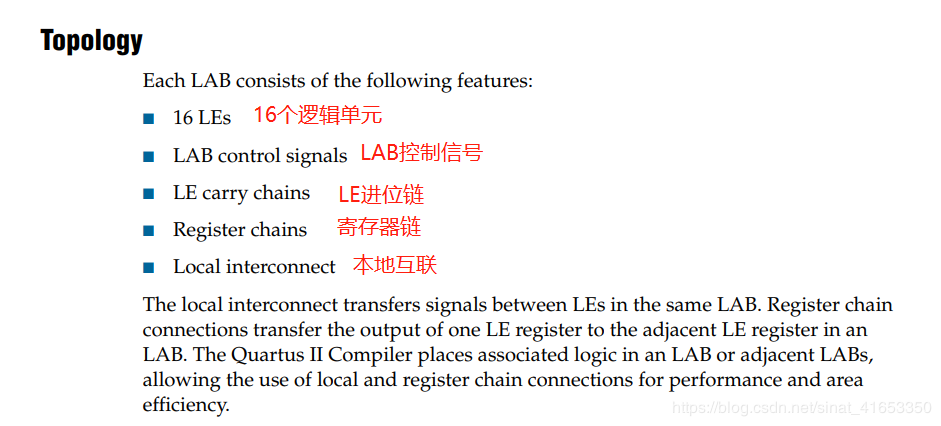

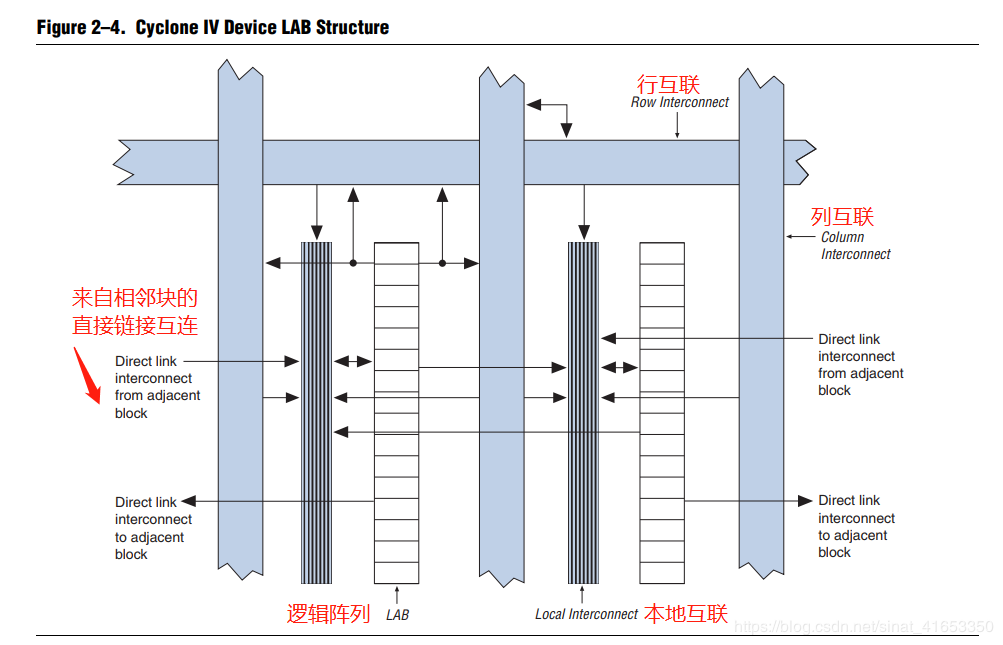

因为逻辑单元(LE)在Cyclone IV器件中是最小的逻辑单元,因此我们可以将多个逻辑单元组合在一起,这就是所谓的逻辑阵列模块(LAB),废话不多说,直接上图,本文基本上是对照器件手册来进行学习,图片较多。

由上图可以得出逻辑单元(LE)组成的逻辑阵列在器件中结构分布,逻辑阵列的控制信号总共有8个(两个时钟,两个时钟使能,两个异步清零,一个同步清零和一个同步加载)。

请记住逻辑阵列的结构布局,后面会汇总各资源在器件的结构图,然后组成整改FPGA器件的资源分布图。

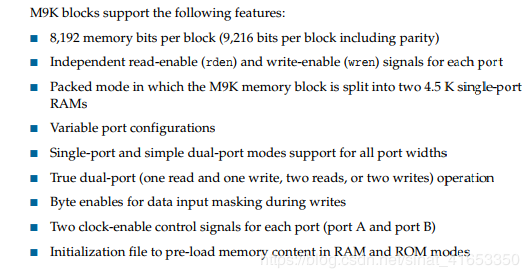

2.嵌入式存储器(Kbits)嵌入式存储器结构由一列列 M9K 存储器模块组成,通过对这些 M9K 存储器模块进行配置,可以实现各种存储器功能,例如:RAM、移位寄存器、 ROM 以及FIFO 缓冲器。

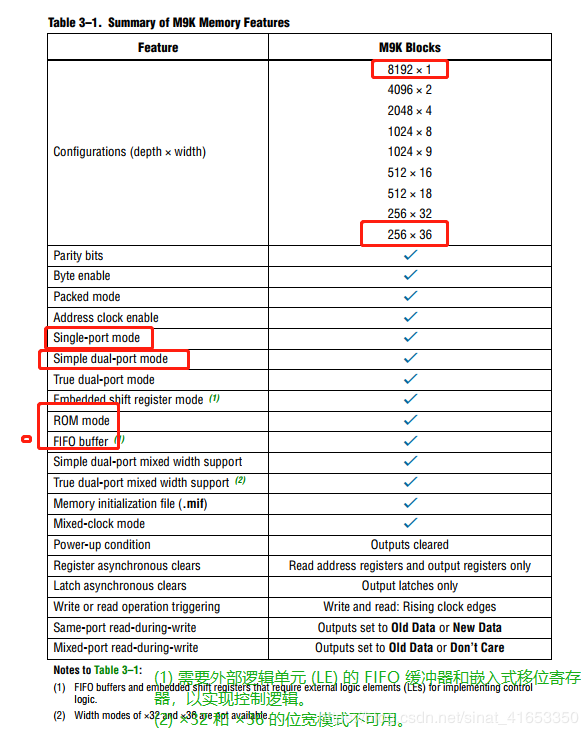

由上表可以得知M9K存储器模块支持最高8192个存储位(包括奇偶校验位的话,每模块共9216位)

上图中提到M9K存储器有用于每一个端口的独立读使能(rden)与写使能(wren信号)。

其中在packed模式下,可以将M9K存储器模块分成两个4.5K的单端口RAM。

具体如何配置何种存储器模式(RAM、移位寄存器、 ROM 以及FIFO 缓冲器),将在下周IP核使用中,详细介绍,

3.嵌入式乘法器

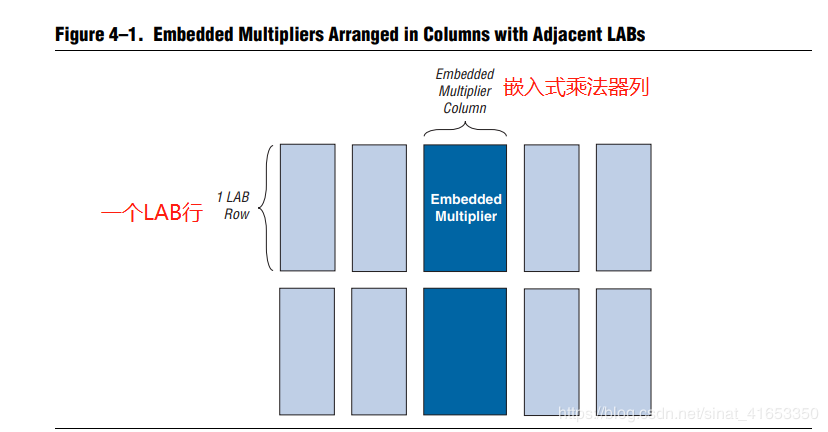

上图展示的是一个嵌入式乘法器列以及相邻的逻辑阵列模块(LAB),乘法器可以配置成一个1818的乘法器,或者配置成两个99乘法器,对于那些大于18*18的乘法运算,Quartus II软件会将多个乘法器级联在一起,虽然没有乘法器数据位宽的限制,但数据位宽越大,乘法运算将会越慢。

其中还可以通过M9K存储器模块用作查找表(LUT)可以实现软乘法器。LUT中存储输入数据同系数乘积的部分结果,可作为DSP的高性能应用,实现了可变深度与宽度的高性能软乘法器,增加了器件的可用乘法器数量。

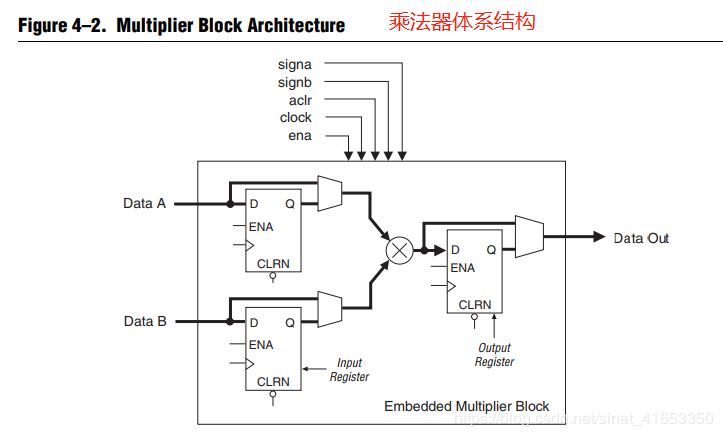

上图表示了乘法器模块的体系结构,发现其组成部分有三个:

1.乘法器级

2.输入与输出寄存器(前几篇文章提到为何需要)

3.输入与输出接口。

上图也清晰的表明了乘法器的操作模式。

乘法器输入信号经过输入寄存器,或者直接以9bit或18bit的形式连接到内部乘法器级,因此输入数据是否经过寄存器可以单独设置,输出寄存器仍是同理。

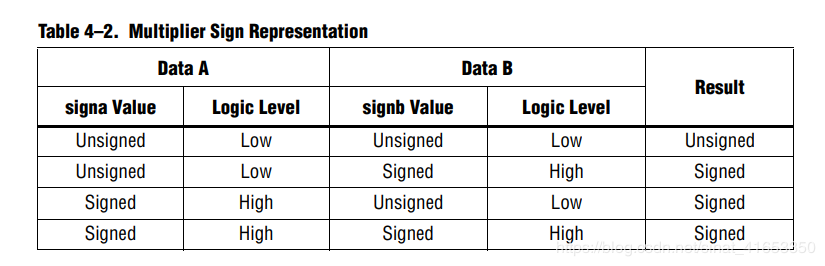

其中乘法器级的每一个操作数都是一个唯一的有符号或者无符号的值。signa与signb控制乘法器输入,并决定值是有符号还是无符号的值,当signa和signb信号如果未使用的话,Quartus II软件会将乘法器默认设置成无符号乘法运算,具体如下表所示。

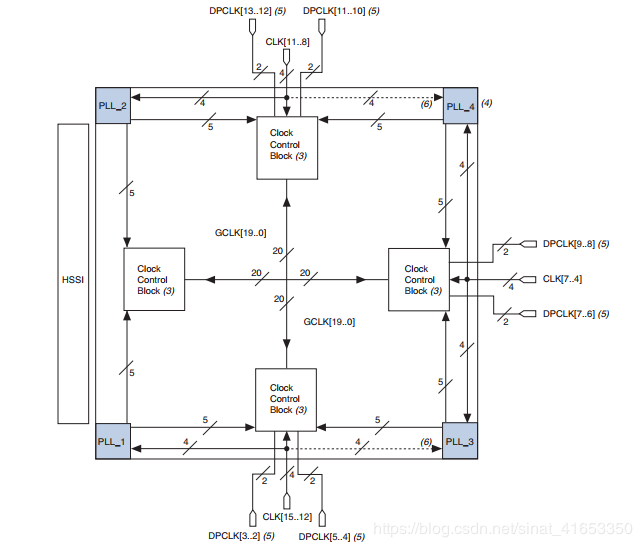

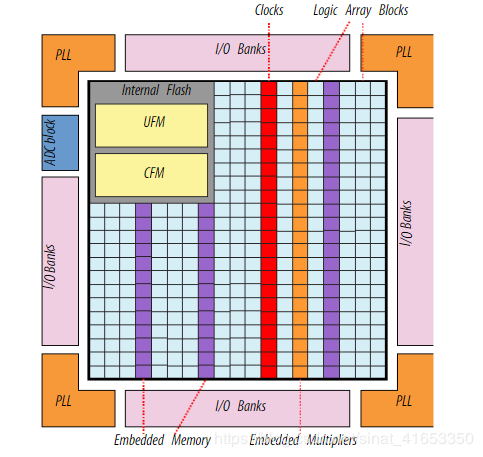

因为长期使用E系列器件,就不详细介绍时钟网络的概念了,但是在GX系列中提出了PLL的模块位置。

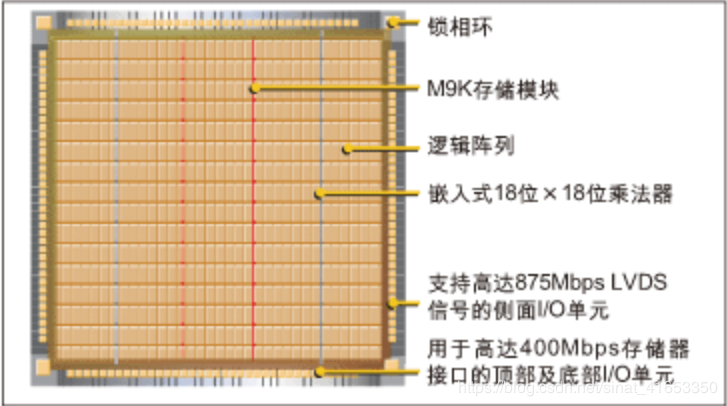

由上图可以看出4个锁相环PLL分布在器件的四周,当外部参考时钟经过器件的顶部或者底部以及右侧的时钟管脚后,进入到FPGA器件后,能够快速的进入到PLL模块,实现最短时钟源路径,从而生成较高的生成时钟质量。另外PLL属于模拟电路,放在器件边缘有利于生产。

PLL作用是能够通过对输入的时钟信号进行分频,倍频以及相位控制,比如相位控制这一作用在SDR SDRAM存储器中得到应用,因为该设计需要用到频率相同,但相位相差180°的时钟信号。除了EP4CE6和EP4CE10两种类型的只含有两个PLL单元外,其余均含有4个PLL。

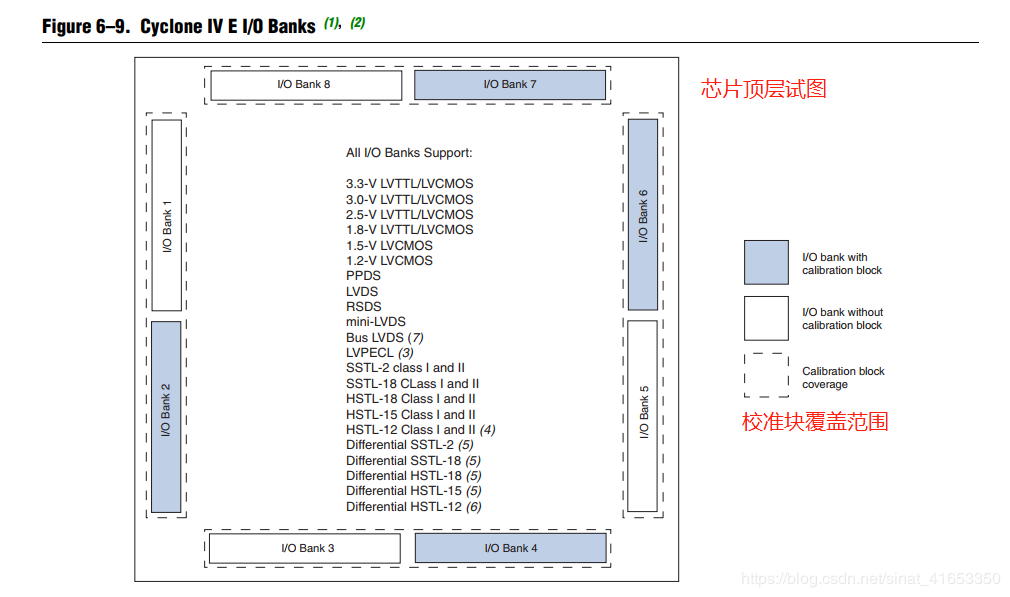

5.用户I/O块

上图看出I/O块分布在器件四周,具体电压,电流标准以及摆率控制参考实际电路选择。

这里提醒Altera推荐的数据流向策略是数据流由左侧I/O输入,然后经过处理(运算和存储),最终由右侧输出。

而控制信号是自上向下的,即控制信号由顶部I/O单元进入,底部I/O单元输出。

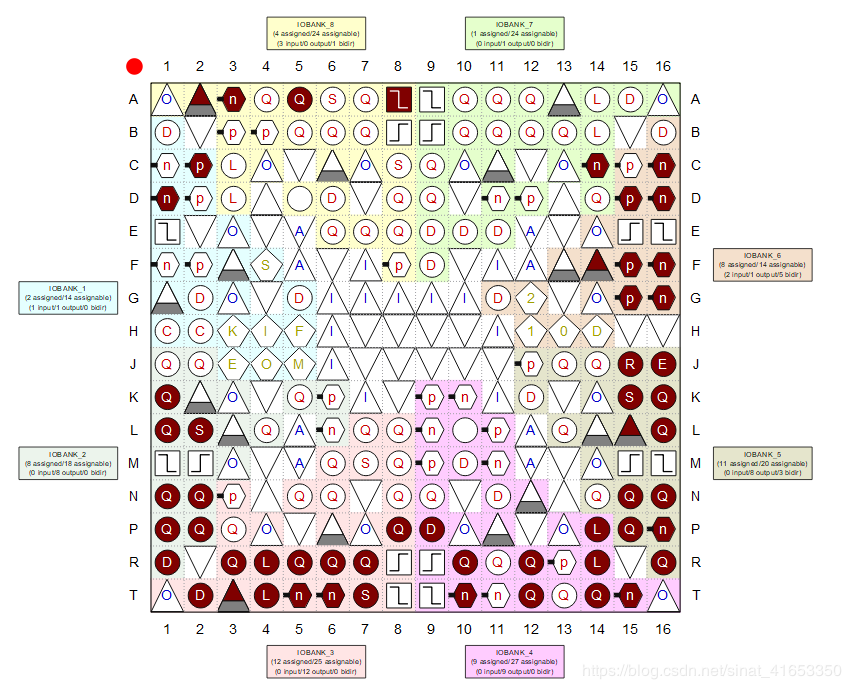

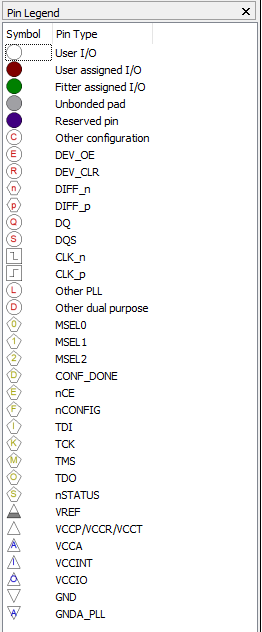

6.Top View下图是Quartus II芯片的顶层视图,这些带符号的究竟代表着怎样的含义呢?

在View–>Pin Legend中打开可得下图对器件的每个符号进行的解释,三角向上的是VCC,三角向下的是地,P和N代表的是差分信号对。

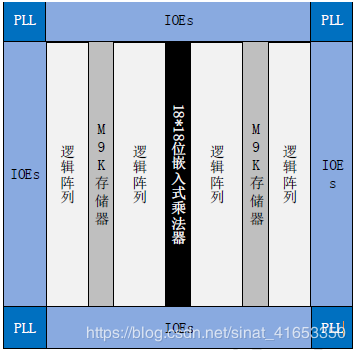

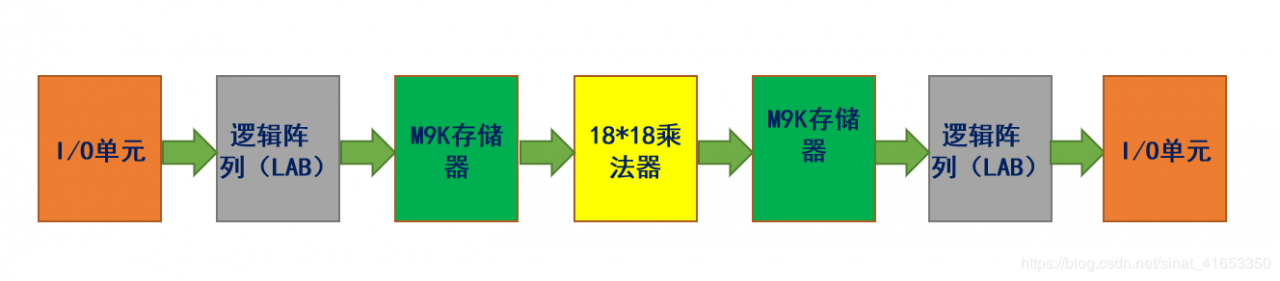

经过上面对器件资源的介绍,那么这些资源如何分布在器件内部呢?下图不同器件资源分布图

这三个资源分布图一对比就清晰看出(三个不属于同一系列器件),逻辑阵列LAB与M9K存储器以及乘法器交替分布,这样可以缩短数据的传输路径,以获得更加优异的时序性能。

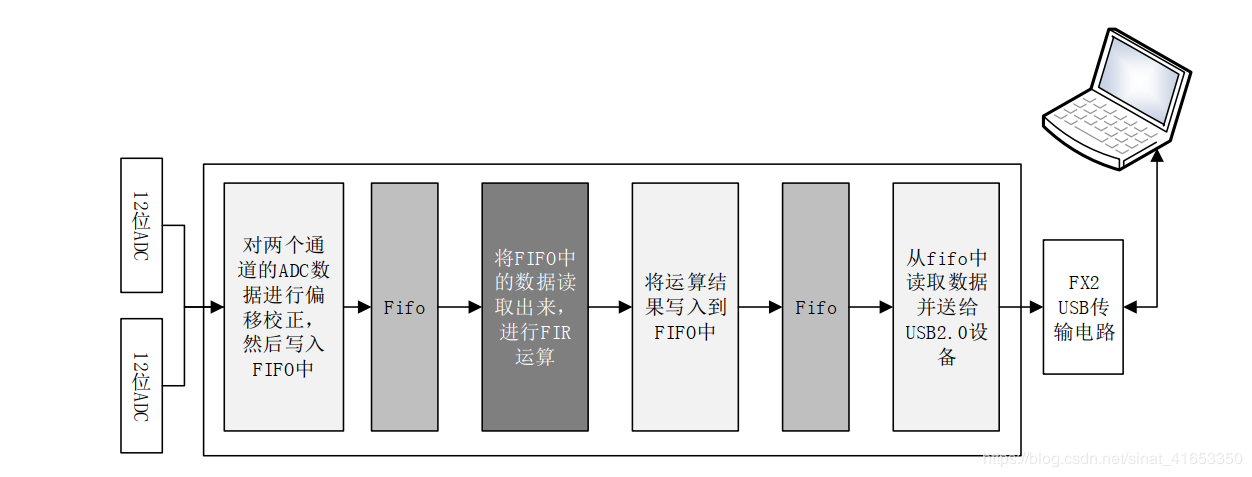

案列分析下面以一个典型的数据采集实例,来分析这种资源分布的优势。

对照上图来分析数据流向:

1.数据先由外部高速ADC采集,通过I/O口进入到FPGA内部。

2.接着经过一定的逻辑电路预处理后写入到由M9K存储器组成的缓存,如FIFO或双口RAM中。

3.然后,再由逻辑电路从M9K存储器中读出,进行相应的处理,在处理的过程中,可能会需要高速的乘法运算,因此该部分数据可以直接送到片上集成的18*18乘法器上进行运算。

4.运算结束后,再由逻辑电路处理后送入由M9K存储器组成的缓存,如FIFO或双口RAM中。

5.等待其他电路如数据发送电路将数据从缓存中读取出来并最终通过I/O口连接的通信电路传输出去。

如果我们将整个数据流从左向右分析,就会发现数据流中每一级所需要的资源都刚好和 Cyclone IV E 中的各个资源的分布位置对应。 因此,按照官方推荐的数据流向策略将上述设计布置到 Cyclone IV E 的对应资源上, 则能够得到时序优化了的布局布线,从而使设计能够工作在较高的时钟频率下。

作者:硬件嘟嘟嘟