【计算机组成原理笔记未完..】第四章 存储器

文章目录4.1 概述4.1.1.存储器的分类1.按存储介质分类2.按存储方式分类3.按在计算机中的作用分类分类4.1.2.存储器的层次结构1.存储器三个主要特性的关系2.缓存 — 主存层次 和 主存 — 辅存层次4.2 主存储器4.2.1概述1.主存储器的组成2.主存和CPU的联系3.主存中存储单元地址的分配4.主存的技术指标4.2.2半导体芯片简介1.半导体存储芯片的基本结构2.半导体存储芯片的译码驱动方式(1)线选法(2)重合法4.2.3随机存取存储器

4.1 概述

TTL(集成低,工耗高,速度块)、MDS (工耗低,集成高) 磁表面存储器 非易失

磁头、载磁体 磁芯存储器 非易失

硬磁材料、磁光材料 光盘存储器 非易失

激光、激光材料 2.按存储方式分类 存取时间与物理地址无关(随机访问)

*随机存储器 [在程序的执行过程中可读可写]

*只读存储器 [在程序执行过程中只读] 存取时间与物理地址有关(串行访问)

*顺序存取存储器 磁带

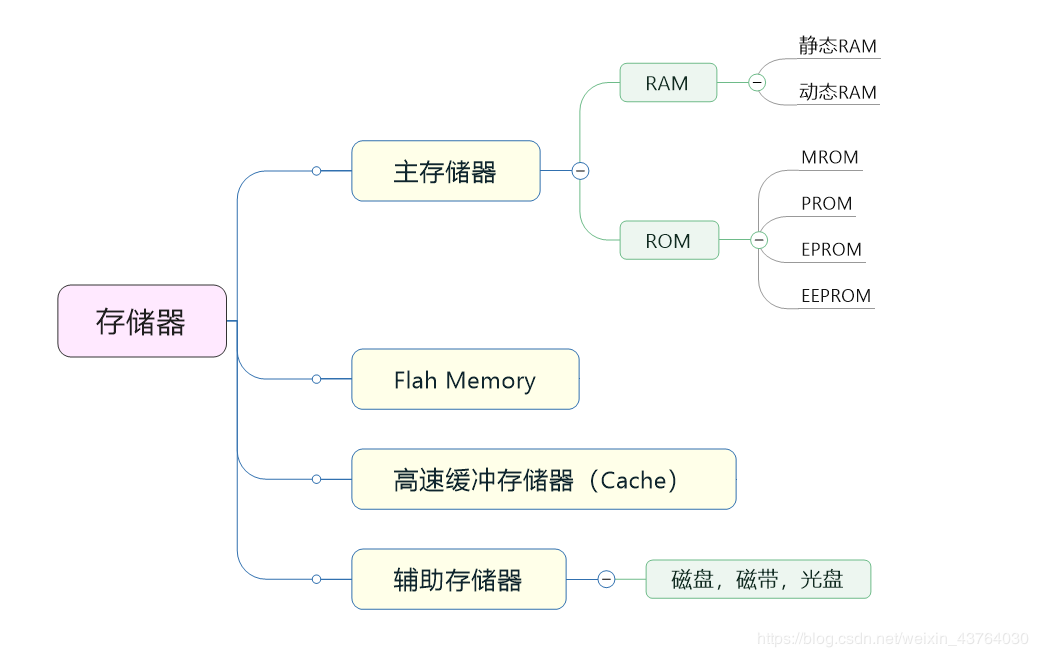

*直接存取存储器 磁盘 3.按在计算机中的作用分类分类

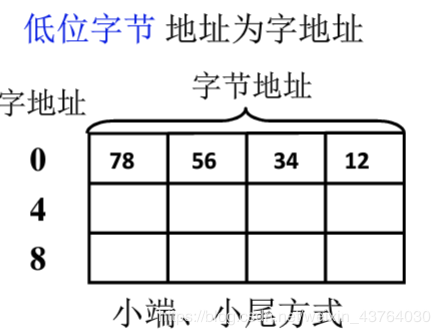

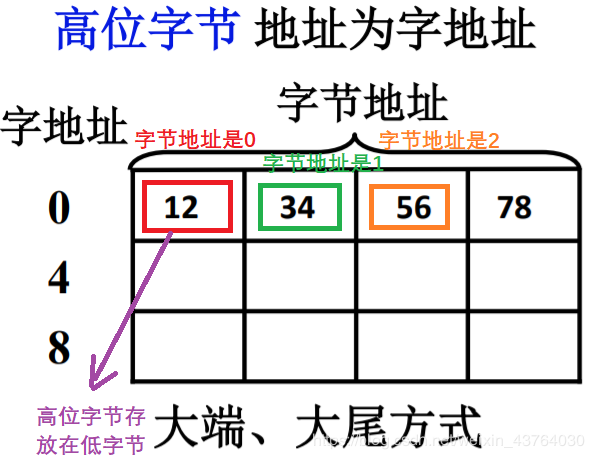

把低位字节的地址作为存储器的地址

把低位字节的地址作为存储器的地址

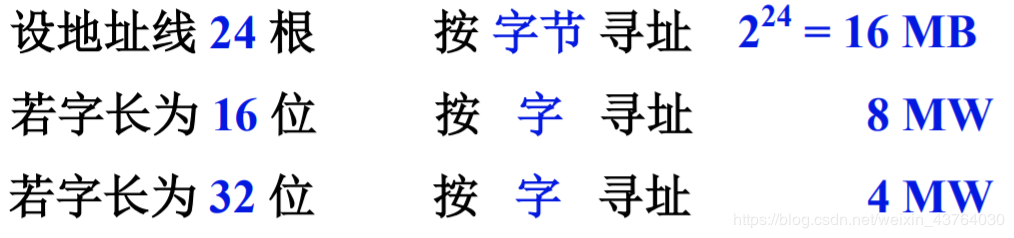

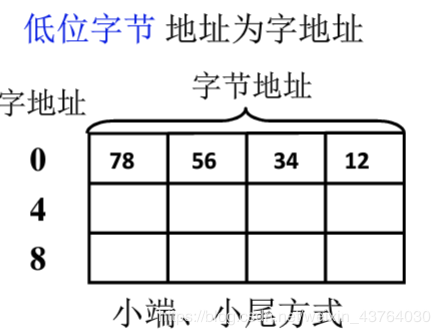

w:word(十六位) 4.主存的技术指标 存储容量 主存 存放二进制代码的总位数 存储速度

*存取时间 从存储器给出地址一直到稳定的数据输出(写出时间),或者是数据输入写入到给定存储单元中(写入时间)

*存取周期 连续两次独立的存储器操作(读或写)所需的 最小间隔时间 存储器的带宽 位/秒 4.2.2半导体芯片简介

作者:陈野菜

主要解决两个问题:

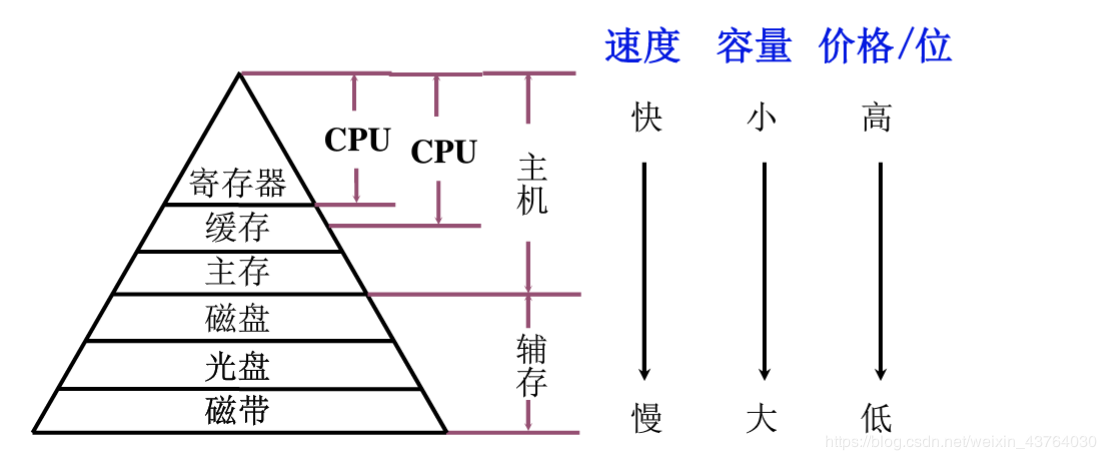

1.存储器可分为哪些类型?

2.现代存储器的层次结构,为什么要分层?

TTL(集成低,工耗高,速度块)、MDS (工耗低,集成高) 磁表面存储器 非易失

磁头、载磁体 磁芯存储器 非易失

硬磁材料、磁光材料 光盘存储器 非易失

激光、激光材料 2.按存储方式分类 存取时间与物理地址无关(随机访问)

*随机存储器 [在程序的执行过程中可读可写]

*只读存储器 [在程序执行过程中只读] 存取时间与物理地址有关(串行访问)

*顺序存取存储器 磁带

*直接存取存储器 磁盘 3.按在计算机中的作用分类分类

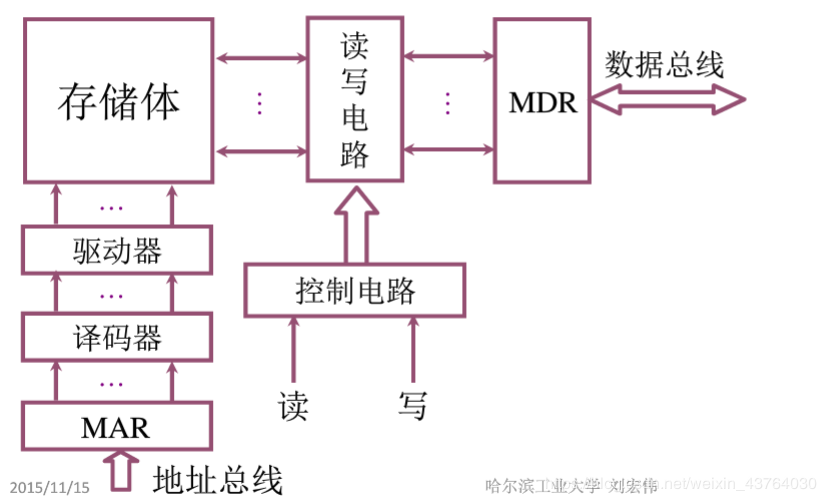

存储体:保存我们的指令和数据

MAR:保存了我们要访问的那个存储单元的地址

(这个地址必须经过译码器译码之后,我们才能选定指定的存储单元)

MDR:保存了我们要读出或写入的数据

(这个数据是读出或写入,要通过读写电路和控制电路来进行控制。如果是写入的话,就把MDR的数据送入到MAR指定的存储单元中,如果是读出,那么指定的存储单元的数据就会送到MDR中)

读写电路:用来控制执行读或写时,数据传输的方向。

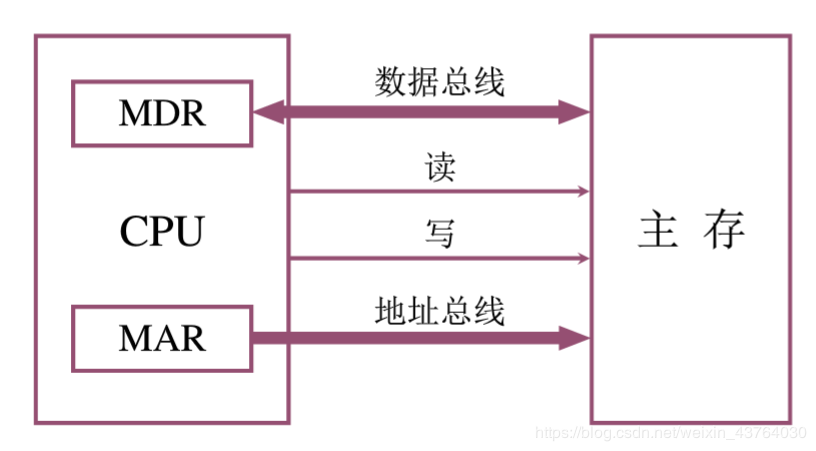

CPU和主存之间的连接信号(3类):

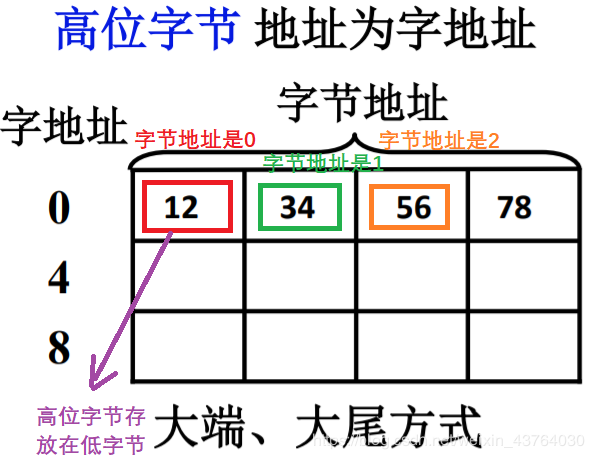

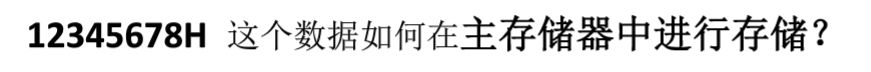

假设现在主存的结构 他的存储字长是32位,也就是说我们对这个存储器某个单元进行读或者写,一次最多可以读出或写入32位0,1。另外我们主存的编址单位是字节,每个字节都有一个地址,在这种情况下,一个存储字为32位,一个字节是8位,都有一个地址,那么:

有两种方式:

把低位字节的地址作为存储器的地址

把低位字节的地址作为存储器的地址

w:word(十六位) 4.主存的技术指标 存储容量 主存 存放二进制代码的总位数 存储速度

*存取时间 从存储器给出地址一直到稳定的数据输出(写出时间),或者是数据输入写入到给定存储单元中(写入时间)

*存取周期 连续两次独立的存储器操作(读或写)所需的 最小间隔时间 存储器的带宽 位/秒 4.2.2半导体芯片简介

两个问题:

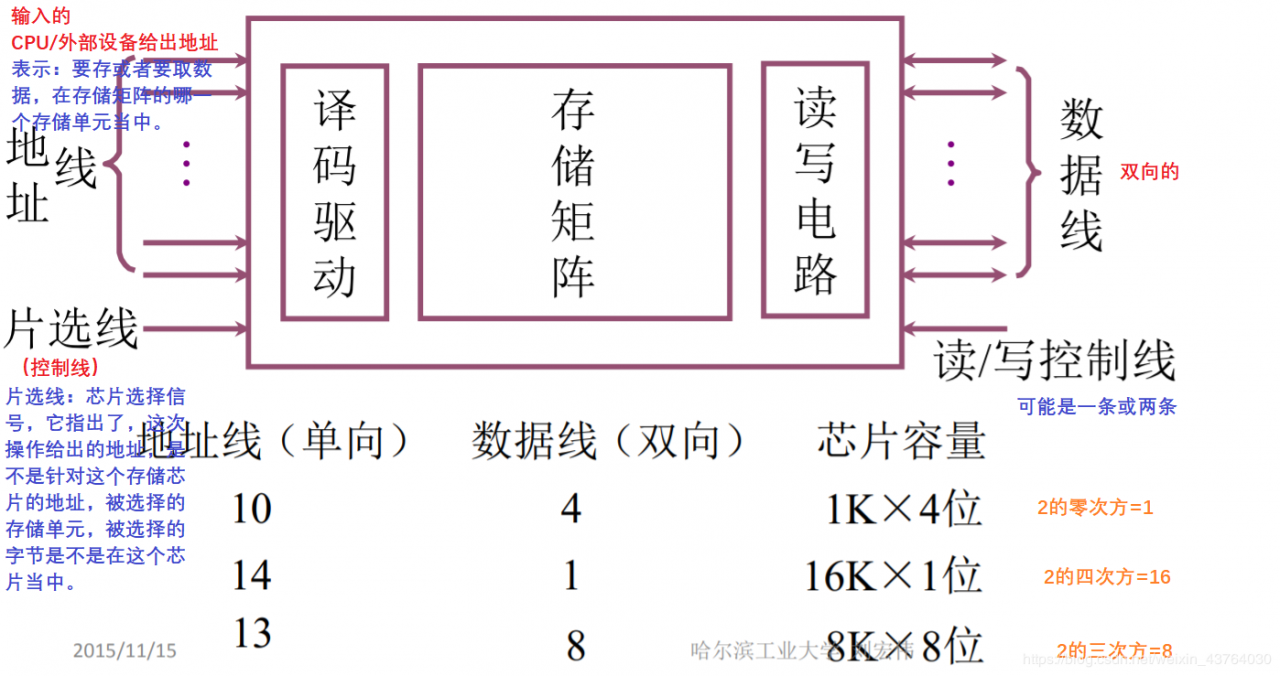

1.半导体存储芯片的基本结构

2.半导体存储芯片的译码驱动方式

(线选法,重合法)

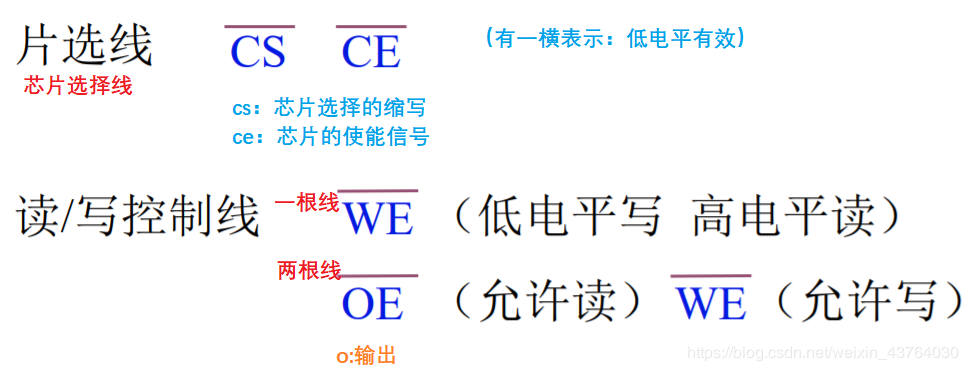

存储芯片片选线的作用

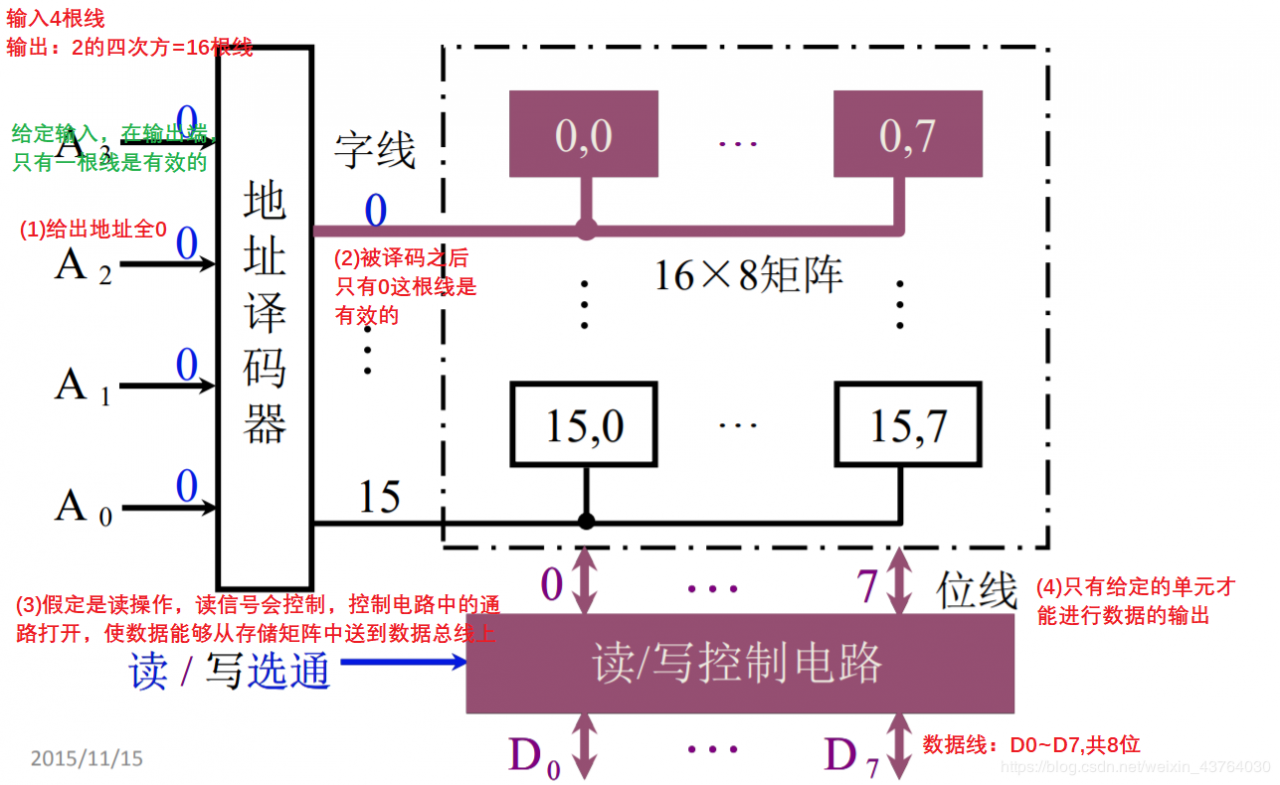

[相当于线性]

A0~A3 四个地址,就是有16个存储单元。由于数据线是从D0~D7,共8位,所以这个存储器是16*8的。

缺点:对容量稍大一点的芯片来说,是非常不合适的。

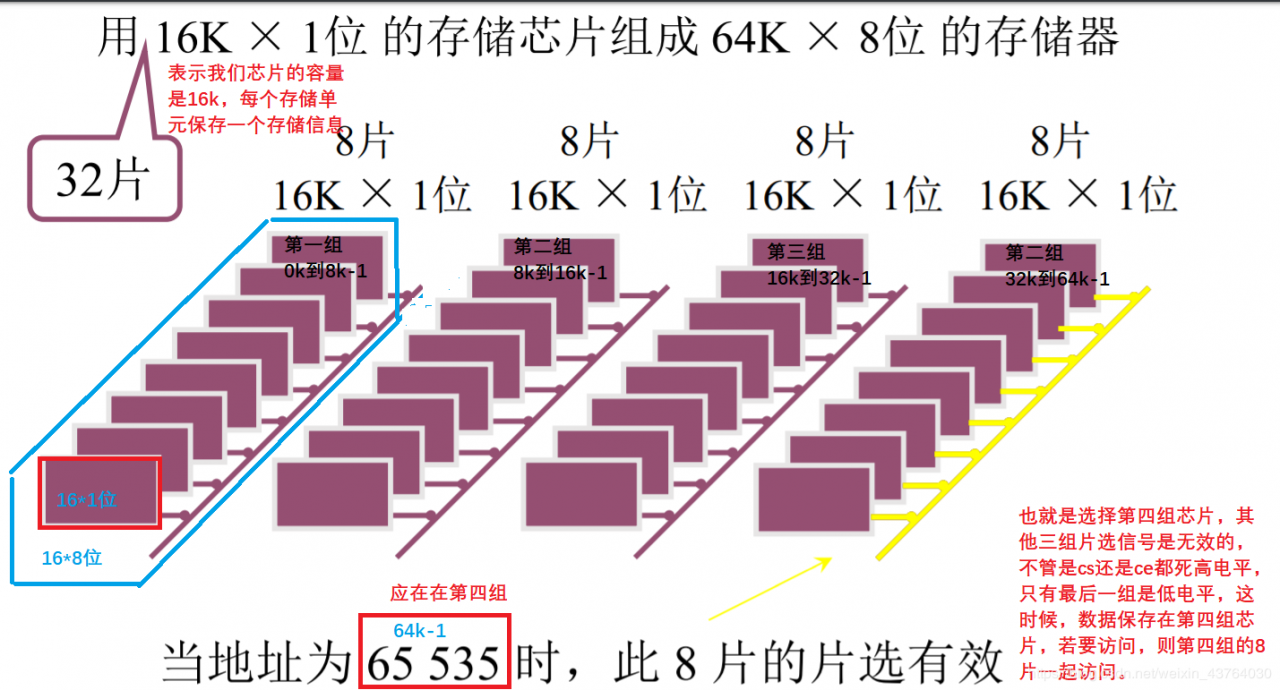

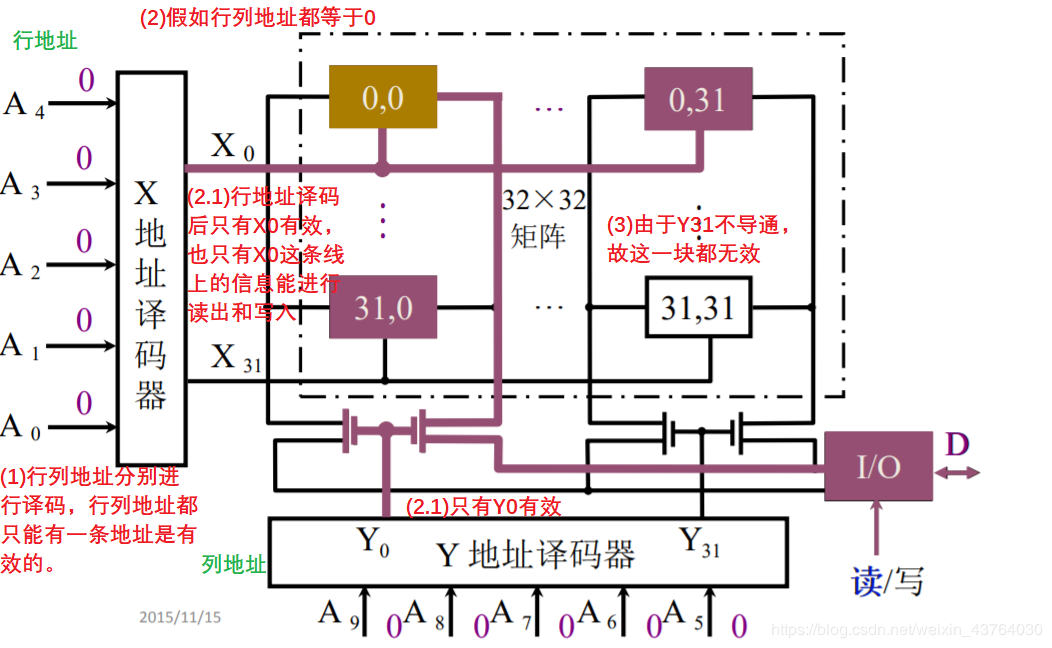

(2)重合法[相当于二维阵列]

两者之间的差异:

如果线选法有20条地址线,这20根地址线有一个译码器来译码,输出是1兆条线

如果用重合法,我们就把20个地址给他分为两部分,假如每一部分都是10位,X方向(行)译码,译出来的线是1K条,列译码也是1K条,总计2K条。比线选法的1赵条小很多。

作者:陈野菜