I2C协议研读(七)

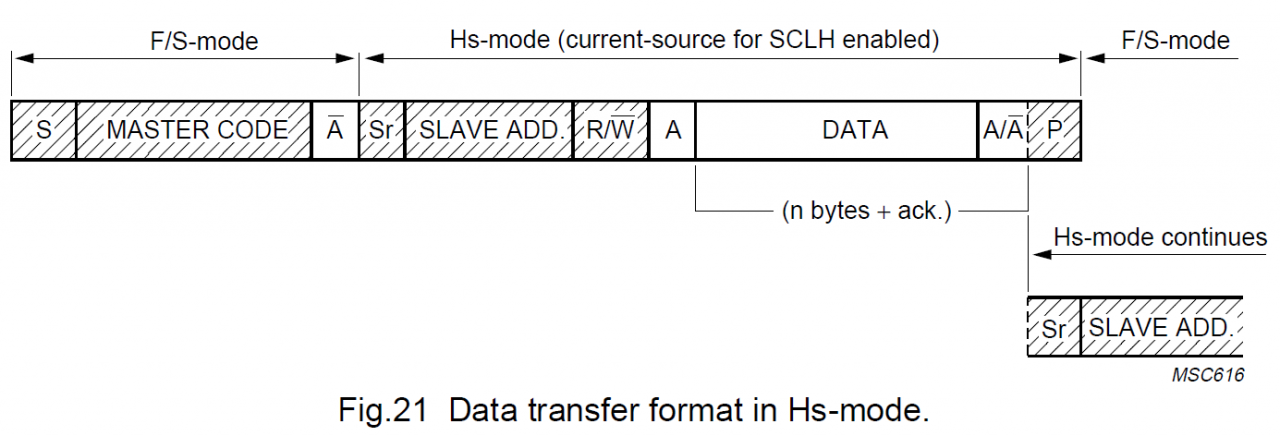

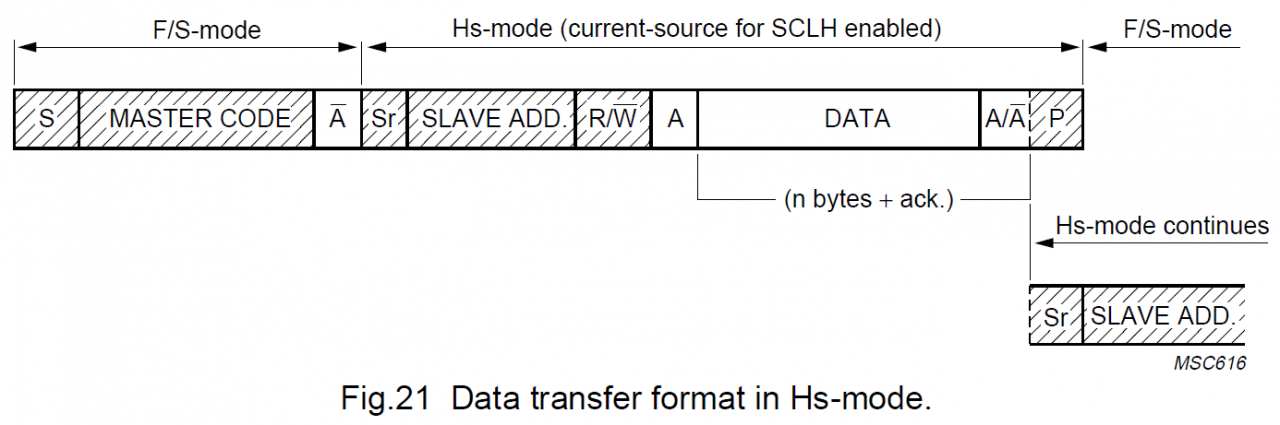

11.2 高速模式下串行数据发送格式:Serial data transfer format in Hs-mode

高速模式下串行数据发送格式符合标准模式I2C总线规范。只有在满足以下条件(所有条件均为F / S模式)后才能启动Hs模式:

1)START 条件(S)

2)8位主机码(00001XXX)

3)非响应位![]()

详细见图

这个主机码有两个主要的功能:

1)在F/S模式的竞争主机之间允许仲裁和同步,产生一个获胜的主机

2)表明高速模式传输的开始

高速模式主机码是保留的8位编码,并不用于从机寻址或其他目的。更进一步,每个主机都有独特的主机码,一根I2C总线上最多可以有8个高速主机(尽管主机码0000 1000 应该保留为测试和诊断)。主机码对高速主机设备来说是可以软件编程的,而且该码是由系统设计者选定。

仲裁和时钟同步只在主机码和非响应位发送期间发生,这是在一个获胜主机保持活跃之后。主机码向其他设备指示将开始Hs模式传输,并且连接的设备必须符合Hs模式规范。不允许任何设备响应主机码,主机码是在非响应位之后。

在非响应位之后,SCLH线上拉到高电平,活跃主机转换到Hs模式并使能电流源上拉电路。由于其他设备可以通过延长SCLH信号的LOW周期来延迟tH之前的串行传输,因此当所有设备都释放SCLH线并且SCLH信号达到HIGH电平时,活动主设备将启用其电流源上拉电路 ,从而加快了SCLH信号上升时间的最后一部分。

活跃主机发送重复START条件和7位(或10位)从机地址和一个读写位,接收被选中从机发来的响应位。

在重复起始条件和每个响应位及非响应位后,活跃主机disable他的电流源上拉电路。这使得其他的设备通过延长低电平来延迟串行传输。当所有设备都释放,SCLH信号到高电平的时候,活跃主机重新使能电流源上拉电路,这样加快了SCLH信号上升时间的最后一部分。

下一个重复开始条件开始后,数据继续以高速模式传输,并在停止条件后切换回F/S模式。为了减少主代码的开销,主设备可能会链接许多Hs模式传输,并以重复的START条件(Sr)分隔。(没太明白,继续看)

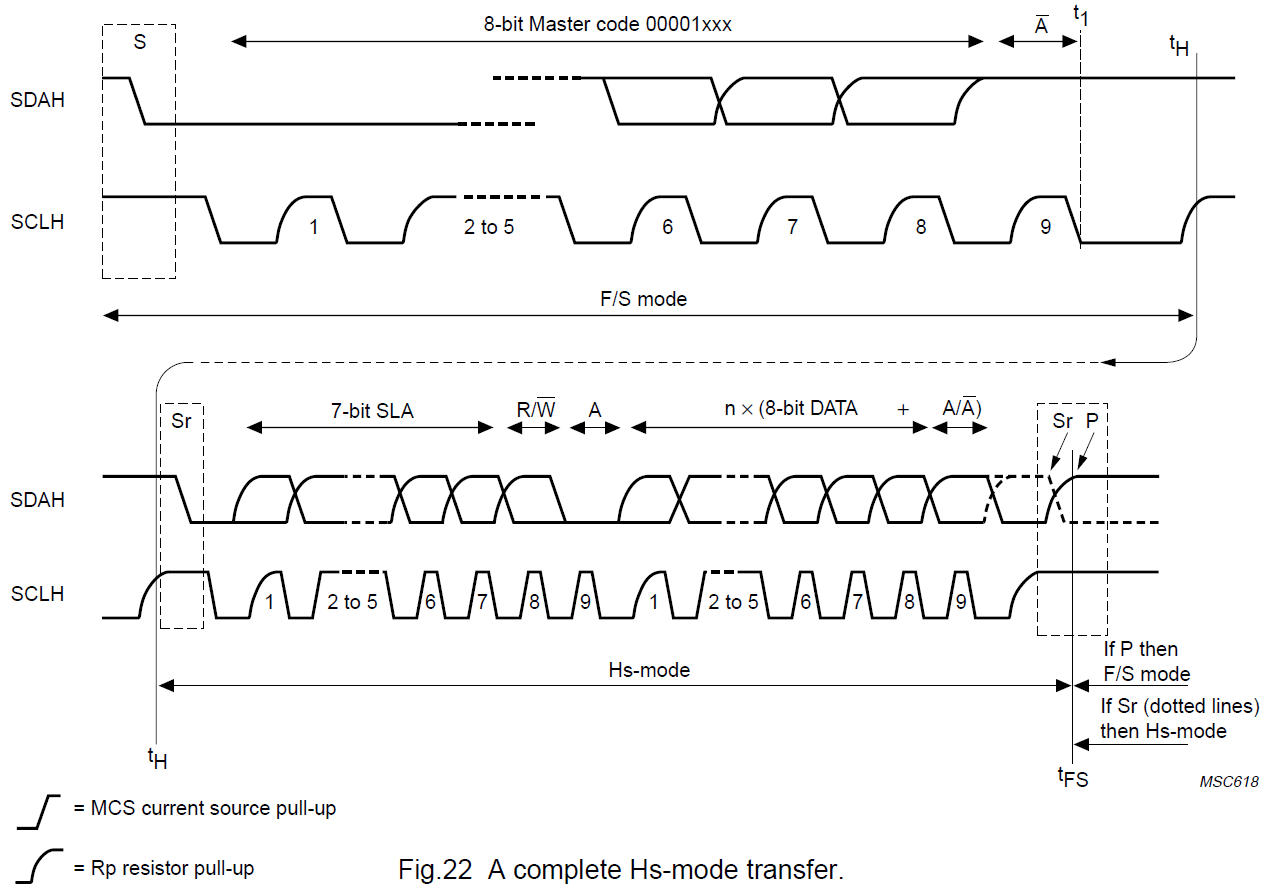

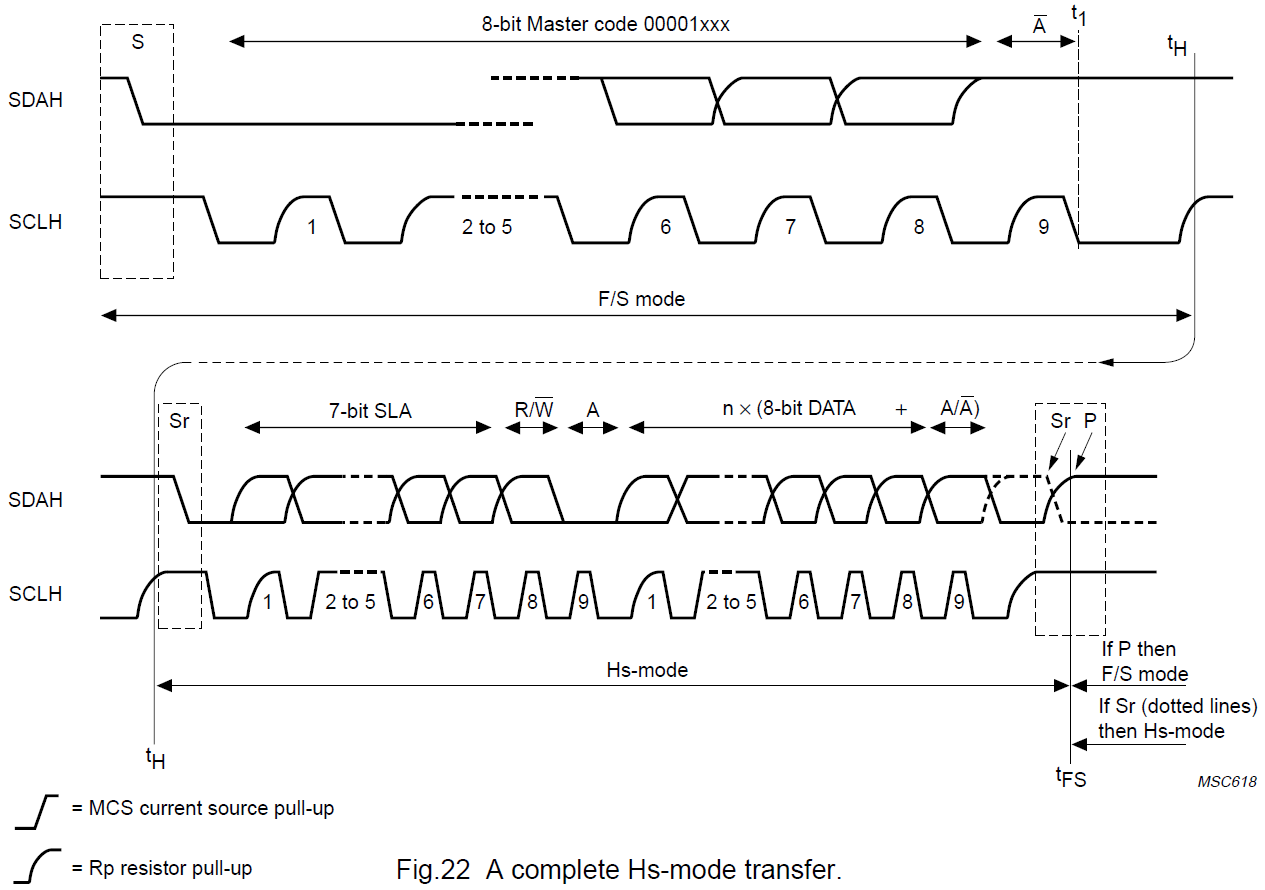

11.3 F/S到Hs模式转换:Switching from F/S-to Hs-mode and back

复位和初始化之后,高速设备必须处于Fast-mode(实际上是F / S模式,因为快速模式与标准模式向下兼容)。每个高速模式设备可以从快速模式转换到高速模式,也可以再转回来,都是由I2C总线的串行传输控制。

在图22中,t1之前,每个连接的设备都支持快速模式。在t1和tH(此刻间隔可以被任意设备延长)之间每个连接的设备必须识别“S 00001XXX A”序列并将内部电路从快速模式设置转换为高速模式设置。t1和tH之间连接的主机和从机设备通过以下动作执行转换。

对于活跃的主机:

1)根据Hs模式下的尖峰抑制要求调整其SDAH和SCLH输入滤波器

2)根据Hs模式要求调整建立保持时间

3)根据Hs模式要求调整其SDAH和SCLH输出斜率控制

4)根据需要在时刻tH后转换到Hs模式比特率

5)在tH使能SCLH输出级的电流源上拉电路

对于非活跃或losing masters:

1)根据Hs模式下的尖峰抑制要求调整其SDAH和SCLH输入滤波器

2)等待STOP条件来检测总线再次空闲的时间

对于所有从机:

1)根据Hs模式下的尖峰抑制要求调整其SDAH和SCLH输入滤波器

2)根据Hs模式要求调整建立保持时间。这个要求可能已经被第一条满足

3)如果需要根据Hs模式要求调整其SDAH输出斜率控制。对于从机设备,斜率控制仅适用于SDAH输出级,而且,根据电路公差(circuit tolerance),快速模式和高速模式的需求无需转换其内部电路就可以满足

在图22中的tFS时刻,每个连接的设备必须识别停止条件(P),然后在t1时刻到来之前将内部电路从高速模式设置转换回快速模式设置。根据快速模式规范,这些操作必须利用最小的总线空余时间来完成。

作者:小孟boy