教你了解存储器

这是我观看了b站up做的笔记

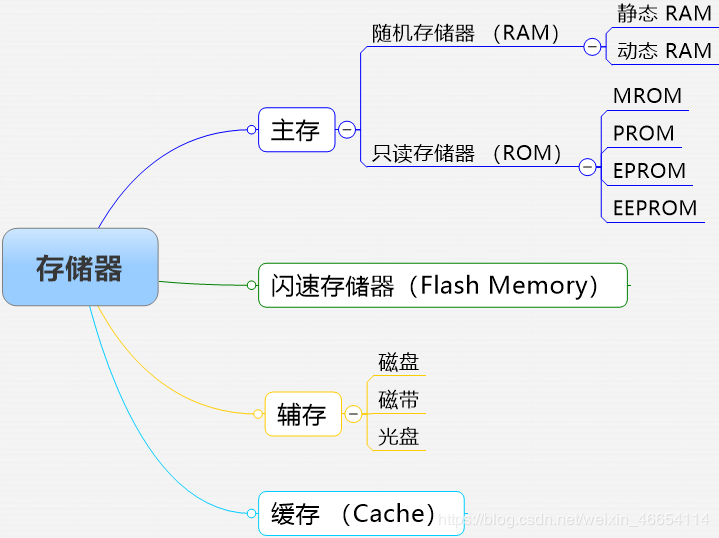

分类:

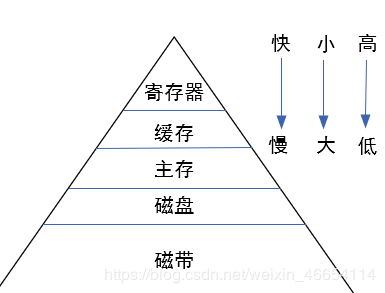

层次结构:

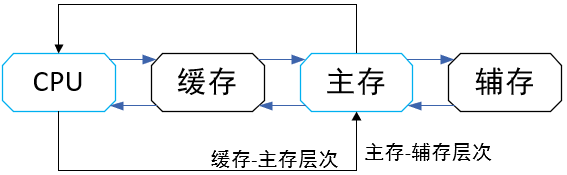

存储层次结构:

存储层次结构:(1)缓存-主存层次:解决CPU和主存速度不匹配问题。

(2)主存-辅存层次:解决容量问题。

(1)存储容量 :指主存能存放二进制代码的总位数,也可用字节总数 来表示。

存储容量=存储单元个数 x 存储字长

存储容量=存储单元个数 x 存储字长/8

(2)存储速度 :由存取时间和存储周期来表示。 2. 半导体储存芯片

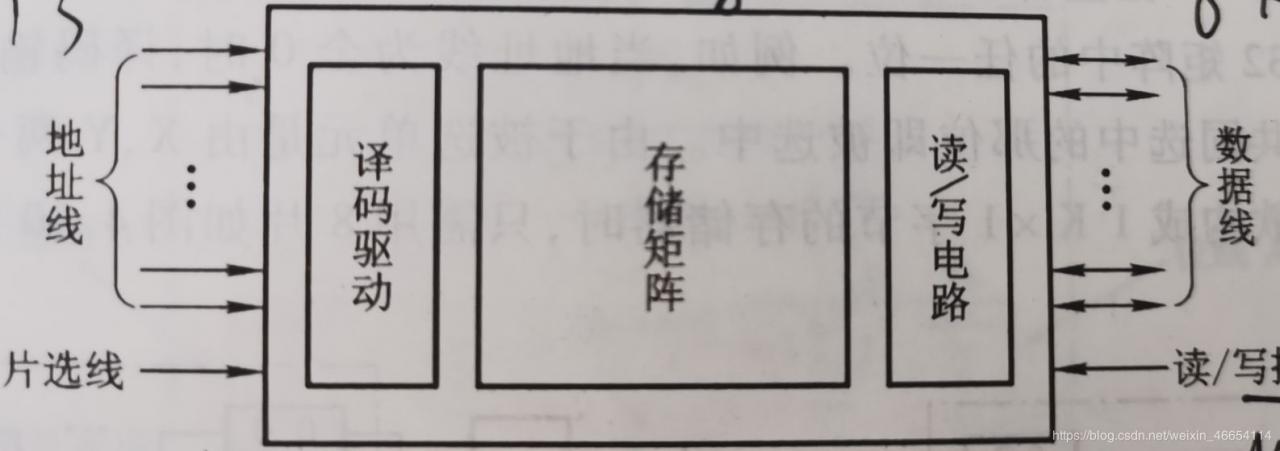

基本结构:

容量:由地址线(单向)和数据线(双向)的位数共同反应。

列:

| 地址线 | 数据线 | 容量 |

|---|---|---|

| 10 | 4 | 2^10(1k)*4 |

| 14 | 1 | 2^14(16k)*1 |

| 13 | 8 | 2^13(8k)*8 |

控制线:

(1)读写控制线:决定芯片进行读写操作。

(2)片选线:用来选择储存芯片。

译码驱动方式:线选法和重合法

DRAM(动态):用在主存

SRAM(静态):用在缓存

| DRAM(动态) | SRAM(静态) | |

|---|---|---|

| 存储原理 | 容量 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 快 | 慢 |

| 刷新 | 有 | 无 |

定义: 一般保存系统程序或系统的配置信息

半导体ROM基本器件:MOS型和TTL型。

CS (片选线 ):连接芯片

WE:读,写

(1)位扩展 : 指增加存储字长(就是增加数据线)。

(2)字扩展 :指增加存储器字的数量,也称存储单元(就是增加地址线)

(3)字,位扩展 :两个都增。

(1)地址线连接:通常将CPU地址线的低位与存储芯片的地址线相连(CPU地址线多于存储芯片地址线)。

(2)数据线连接 : 若存储芯片与CPU的数据线不相等,就对存储芯片进行扩位(使他们数据位数相等)。

(3)读 / 写命令线连接 :高电平为读,低电平为写。

(4)片选线连接 :是CPU与存储芯片正确工作的关键。片选有效信号与CPU的访存信号MREQ(低电平有效,有效时,这次访问的地址才在存储器当中)有关。

(5)合理选择存储芯片 :ROM存放系统程序,RAM为用户编程设计。

解题步骤

(1)写出对应的二进制地址码

(2)确定芯片数量及类型

(3)分配地址线

(4)确定片选信号

(5)确定片选逻辑

目的:提高主存的存取速度

多体并行系统:采用多体模块组成的存储器。

主要作用:解决主存与CPU速度不匹配的问题。

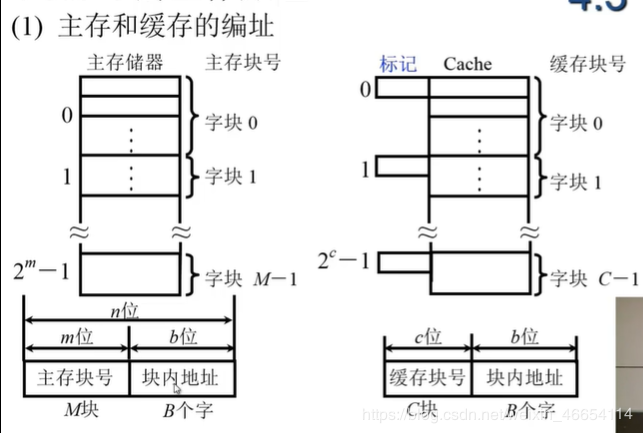

工作原理 主存由2^n个可编译的字组成,每个字有唯一的n位地址 主存 和 缓存以块 为单位存储。 块的大小相同

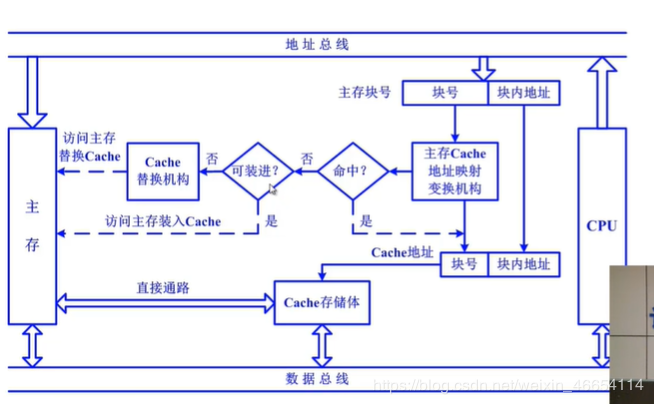

两种情况(1)所需字已在缓存中,可直接访问Cache(一次送一个字节)。

(2)不在,将改字所在的主存整个字块调到缓存。 命中率

(1)Cache 容量越大 CPU命中率越高。

(2)命中Cache:说明主存快已经调入缓存中。

(3)未命中:未调入。 基本结构

(1)Cache存储体。

(2)地址映射变换机构

(3)替换机构

(4)Cache的读写操作

2.Cache–主存地址映射和替换策略

2.Cache–主存地址映射和替换策略

映射机构:主存的块可以放到缓存那些块当中。

替换机构:完成了主存当中的一个块在Cache当中的查找操作。

算法:

先进先出(First-In-First-out,FIFO)算法。 近期最少使用(Least Recently Used,LRU)算法。 四.辅助存储器(外部存储器)特点:不直接与CPU交换信息

与主存一起组成了存储器系统的主存-辅存层次

作者:RodamChen