虚拟存储器

计算机的CPU在运行过程中都是访问内存的,但是如果一个程序的大小超过了内存的大小怎么办、为了解决这个问题。提出了虚拟存储器的概念。让计算机可以访问的内存空间比实际的物理主存要大。

目录

基本原理

访问流程

TLB 地址后备缓冲器。

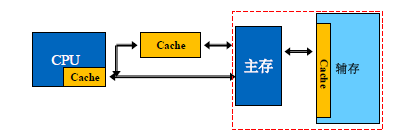

基本原理主要的实现思路和Cache的原理是差不多的。也是利用局部性原理,将部分可能会访问的大容积慢速的辅助存储空间的数据存放到主存中。因为我们每次访问的主存数据不会太大,我们不需要提供完整的主存数据,只需要把需要的数据放在主存中就行。

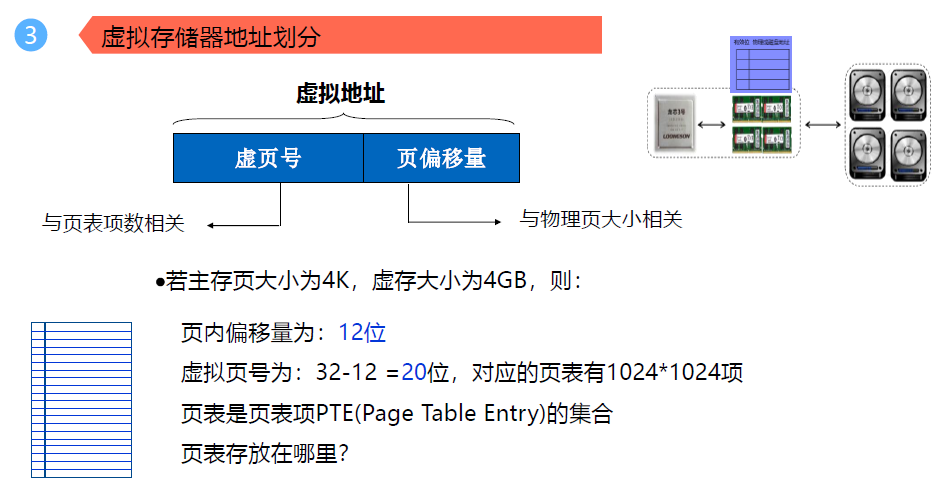

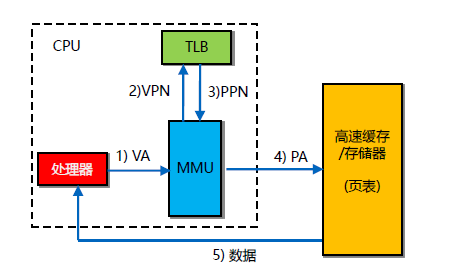

如下图所示,计算机的CPU提供一个虚拟的地址 VA (Virtual Address),虚拟的地址进过MMU存储单元管理器(Memmery Manage Unit)把虚拟的地址VA转换物理的地址PA (Physical Address),这个地址是实际的主存的地址。通过这个就可以访问实际的数据。

VA地址可以分成两个部分,一个是VPN 虚拟页号,一个是VPO 页内数据偏移。每当提供一个地址后,会通过VPN到页表项的 PTE里面去查找这个虚拟页号对应的行数,如果有效位数为1,表明该数据以及在内存中了,如果有效位数为0表明该数据不再内存中。

如果在内存中的话,那么就可以去取该行中存放的我们想要访问的虚拟页号的所对应的实际的物理页号(PPN)。虚拟的每个页号的大小和内存中的页中的大小是一样的,所以VPO 虚拟页内偏移地址和PPO 物理页内偏移地址是一样。所以将该物理页号和页内偏移地址一组合就是完整的实际的物理地址了。

如果不在内存中的话,就要到速度更慢的辅助存储器也就是硬盘等里面将部分主存的页表项替换掉,然后就可以访问了。

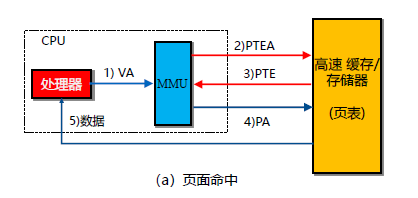

如果是普通的虚拟内存的访问,那么流程是如下图所示的:

如果是命中的流程的话,首先,CPU发出VA虚拟地址,通过MMU存储管理器获得获得页表项的某个项的内存地址,去访问内存,获得实际的要访问的数据的物理页号,该页号和页内的偏移地址组合获得数据的物理地址,然后就可以获取数据了。

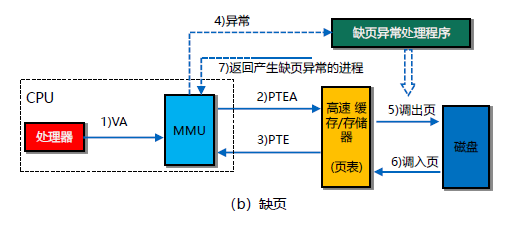

要是没有命中的话,那就更加麻烦了。会产生一个异常,然后会进行缺页处理。从辅存中调出页内数据替换到内存中。然后重新访问获取数据。

可以看到CPU获取数据要访问内存两次以上,消耗了大量的时间,为了解决这个问题就引入了TLB(Translation Lookaside Buffer)地址后备缓冲器。

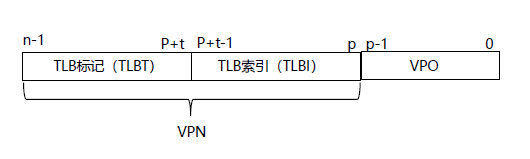

TLB 地址后备缓冲器。这个东西和Cache的映射原理差不多,就是将VPN虚拟页号进行再一次的划分,划分成TLBT(TLB的Tag部分)和TLBI(TLB的指示部分)。通过TLBI将数据映射到TLB上,通过TLBT进行数据的查找。因为TLB可以用类似于Cache的高速存储器来做,所以速度会快的很多。从而减少内存的访问,减少总的数据读取时间

这样的话,就可以少访问一次内存,可以先通过MMU存储器管理单元去访问TLB地址后备缓冲器 获取PPN物理页地址数 ,然后和VPO页内偏移地址组合一下,组成PA 时间的物理地址去访问内存

作者:天马行空_online