随机存取存储器RAM简介

随机存取存储器

静态随机存取存储器SRAM

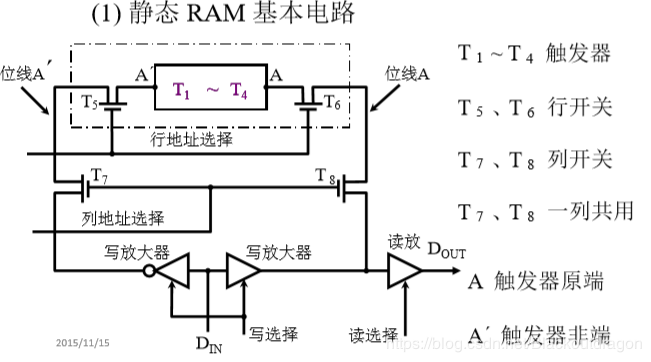

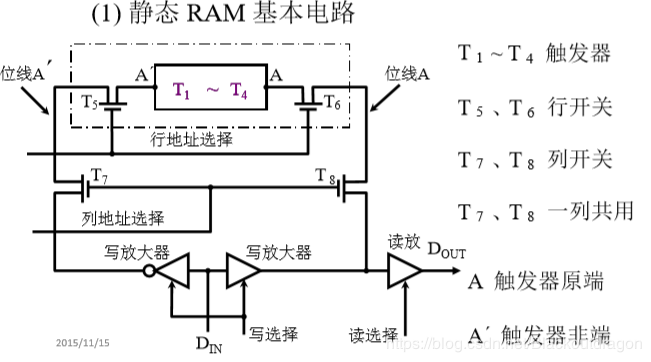

基本单元电路结构

存储0和1信号的方式:T1~T4双稳态触发器,不移丢失或者是损耗,双稳态触发器的左端保持输入信号的非,右端保存原输入信号

移码驱动方式:重合法——分别通过行地址和列地址的联合选中才能输出,每一份存储单元都对应一个行列地址坐标(行地址X,列地址Y)

T5和T6是行地址选择开关

当接通的时候,对应的信号可以通过两端分别经过行选择开关输出到列选择开关终止

T7和T8是列地址选择开关

当开关接通时,允许数据从双稳态触发器两端输出,经过行地址选择器,再通过列地址选择器,实现最终的输出

读写开关,通过输入对应的读写控制信号选择是否打开,通过数据。

总结:

一个SRAM的基本单元需要由8个电路基本元件构成

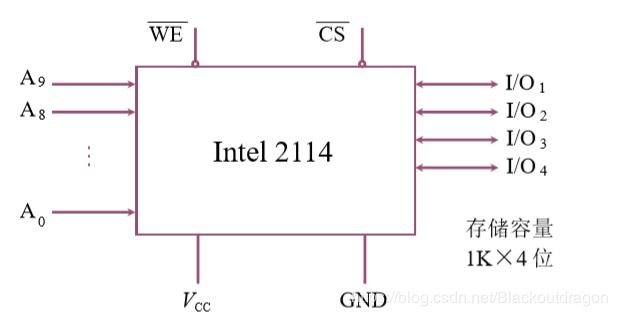

静态芯片举例——Intel2114外特性

存储0和1信号的方式:T1~T4双稳态触发器,不移丢失或者是损耗,双稳态触发器的左端保持输入信号的非,右端保存原输入信号

移码驱动方式:重合法——分别通过行地址和列地址的联合选中才能输出,每一份存储单元都对应一个行列地址坐标(行地址X,列地址Y)

T5和T6是行地址选择开关

当接通的时候,对应的信号可以通过两端分别经过行选择开关输出到列选择开关终止

T7和T8是列地址选择开关

当开关接通时,允许数据从双稳态触发器两端输出,经过行地址选择器,再通过列地址选择器,实现最终的输出

读写开关,通过输入对应的读写控制信号选择是否打开,通过数据。

总结:

一个SRAM的基本单元需要由8个电路基本元件构成

静态芯片举例——Intel2114外特性

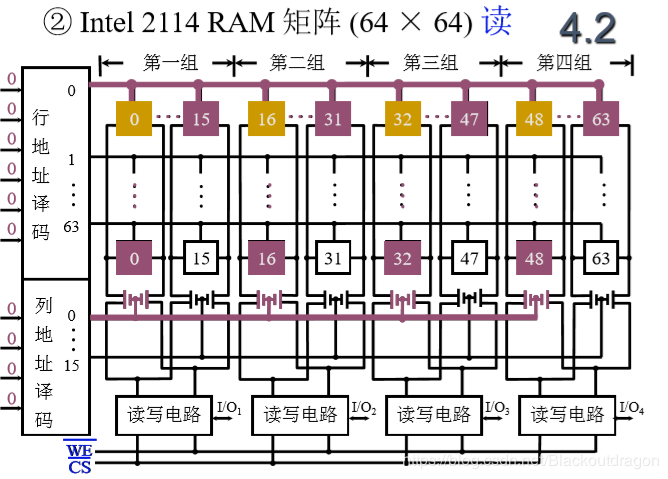

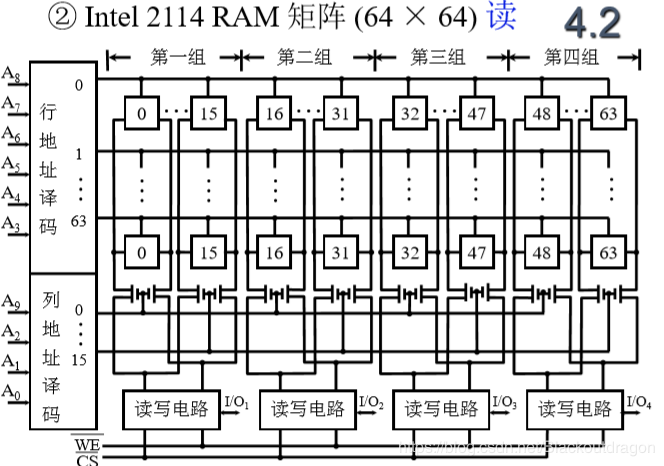

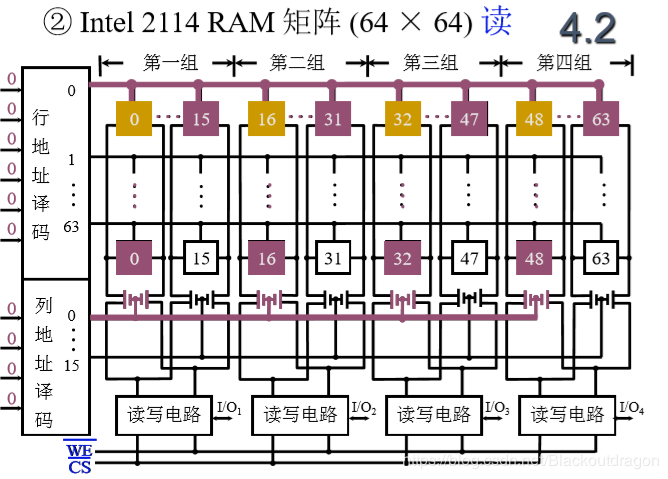

* 输入000000 作为行地址,决定的是第0行进行输出,输入0000作为列地址,决定输出每一组的第0列,对应就是第0列,第16列,第32列,第48列,对外进行输出,造成了每一次地址输出四位数据。 动态随机存取存数器DRAM

作者:~梦醒~

存储0和1信号的方式:T1~T4双稳态触发器,不移丢失或者是损耗,双稳态触发器的左端保持输入信号的非,右端保存原输入信号

移码驱动方式:重合法——分别通过行地址和列地址的联合选中才能输出,每一份存储单元都对应一个行列地址坐标(行地址X,列地址Y)

T5和T6是行地址选择开关

当接通的时候,对应的信号可以通过两端分别经过行选择开关输出到列选择开关终止

T7和T8是列地址选择开关

当开关接通时,允许数据从双稳态触发器两端输出,经过行地址选择器,再通过列地址选择器,实现最终的输出

读写开关,通过输入对应的读写控制信号选择是否打开,通过数据。

总结:

一个SRAM的基本单元需要由8个电路基本元件构成

静态芯片举例——Intel2114外特性

存储0和1信号的方式:T1~T4双稳态触发器,不移丢失或者是损耗,双稳态触发器的左端保持输入信号的非,右端保存原输入信号

移码驱动方式:重合法——分别通过行地址和列地址的联合选中才能输出,每一份存储单元都对应一个行列地址坐标(行地址X,列地址Y)

T5和T6是行地址选择开关

当接通的时候,对应的信号可以通过两端分别经过行选择开关输出到列选择开关终止

T7和T8是列地址选择开关

当开关接通时,允许数据从双稳态触发器两端输出,经过行地址选择器,再通过列地址选择器,实现最终的输出

读写开关,通过输入对应的读写控制信号选择是否打开,通过数据。

总结:

一个SRAM的基本单元需要由8个电路基本元件构成

静态芯片举例——Intel2114外特性

* 输入000000 作为行地址,决定的是第0行进行输出,输入0000作为列地址,决定输出每一组的第0列,对应就是第0列,第16列,第32列,第48列,对外进行输出,造成了每一次地址输出四位数据。 动态随机存取存数器DRAM

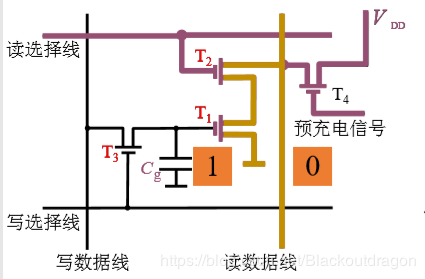

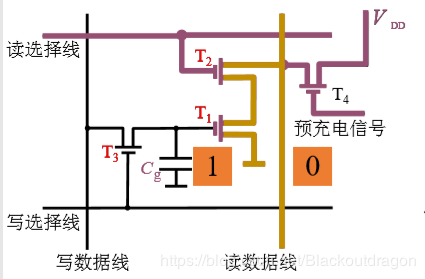

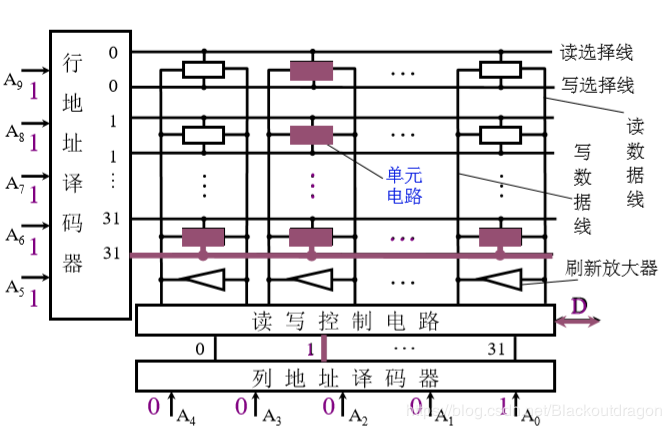

基本单元电路结构:

三管DRAM

电容Cg:最为存储单元,存储0和1信息,有电是1,没电是0

T3:由写选择线进行控制,控制写数据,

T2:由读选择线进行控制,控制读数据

T1:由Cg存储的信号决定

* 有电时,T1打开,在T2读开关打开的情况下,读数据线读的是低电位0

* 没电时,T1关闭,在T2读开关打开的情况下,都数据线读的是Vdd高电位,输出是1

* 总结:读数据线,读出的数据总归是与真实的数据相反,电容内存的是0,读出是1;电容内存的是1,读出就是0

总结:一个动态的随机存取存储器DRAM是由三个基本电路元件构成(不算电容),耗电量极小

三管DRAM芯片举例——Intel 1103

| 分类 | 存储0和1信号量的原理 | 芯片引脚数量 | 集成度 | 功耗 | 速度 | 价格 | 作用 |

|---|---|---|---|---|---|---|---|

| SRAM(静态随机存储器) | 双稳态触发器 | 数量多 | 低,体积较大 | 由于内部结构复杂,输入输出都要长时间运转大量的部件,功耗大 | 速度快(几位地址,就相应的有几根地址线) | 结构复杂,要求部件多,价格高 | 作为高速缓存(由于速度快) |

| DRAM(动态随机存储器) | 电容的充放电 | 数量少 | 高,体积较小` | 内部结构较为简单,输入输出运转部件较少,功耗较小 | 速度慢(内部寻址线少于地址线,需要寄存器进行转换) | 结构简单,要求部件少,价格低 | 作为主存(速度慢,结构简单,容量大) |

作者:~梦醒~