目录

一、原理图阶段

(1)网标连通完整性

二、PCB阶段

(1)基本原则

(2)电源平面层叠

(3)载流能力

(4)规则设置

(5)整体布局

(6)差分走线

(7)敷铜

(8)快捷键(Altium Designer)

(9)后期检查

笔记是思考的迭代积累。

目的:资源积累

方式:熟练的写关键词、使用不多但重要的(通常理解不太深刻),名词解释

欢迎大家互相交流,共同促进理解,提升专业技能。

一、原理图阶段

(1)网标连通完整性

网标浮地:编译原理图,提前调出查看message;

两处网标不一致(例如空格和下划线混淆):打开“参数管理器(参数选择:网络)”,查看该网标的使用频次,仅仅只使用了一次的自建网标(不是芯片管脚自己的网络)要特别注意,逐一排查;

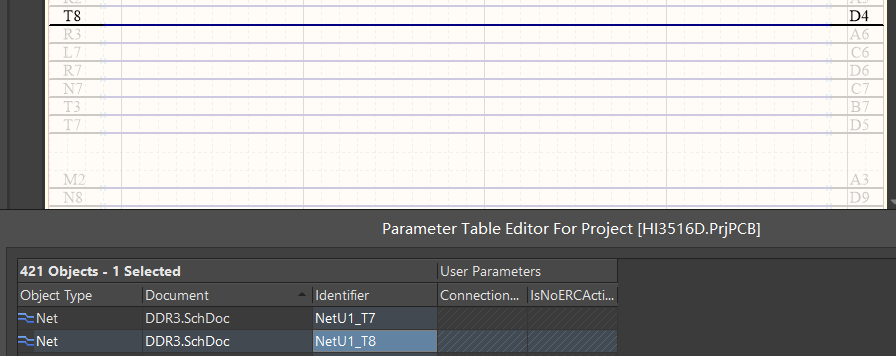

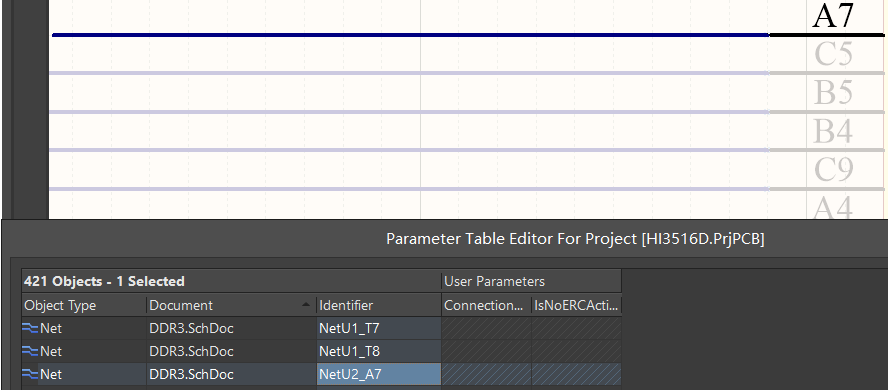

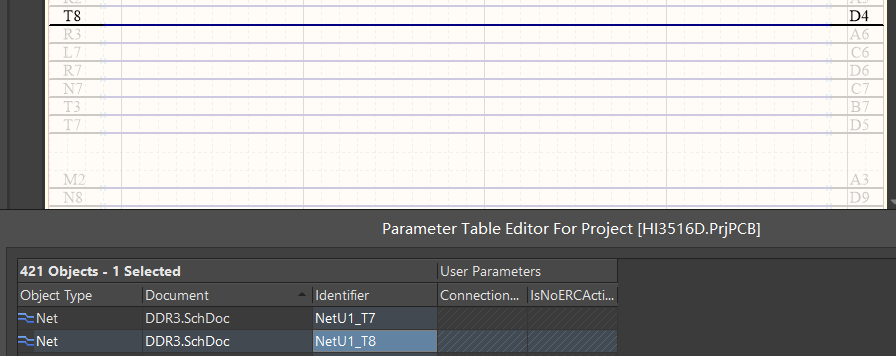

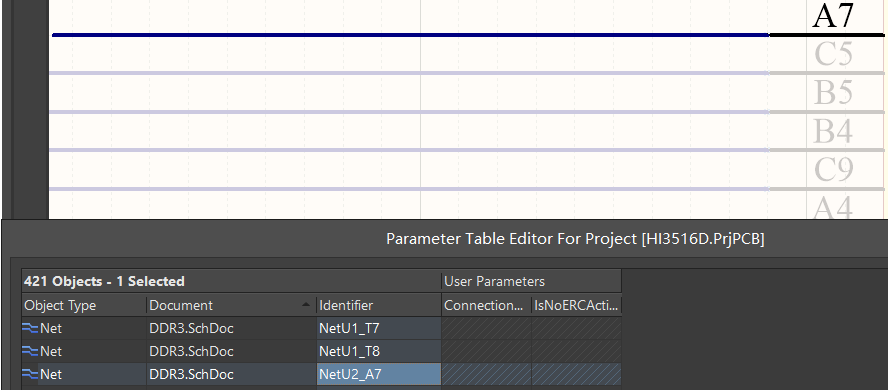

直接连线没有联通(中间断了一小截):逐一排查,需要手动一个个双击identity,这种的命名一般为NetU1_A8(u1芯片的A8引脚)。若有连接,则弹窗为两个引脚联通视图;若没有连接,则弹窗为一个引脚视图。如下图1、2。

图1 弹窗为两个引脚联通视图_T8&D4

图1 弹窗为两个引脚联通视图_T8&D4

图2 弹窗为单个引脚视图_A7

二、PCB阶段

(1)基本原则

20H原则

原因:电源平面和地平面相互耦合RF能量,导致边缘磁通泄露;

期望:抑制边缘辐射效应,提高EMC,使得电场只在gnd层范围内传导;

10H磁通泄露显著改变,20H抑制70%,100H抑制98%;

不知道gnd和power的实际间距,建议内缩50mil;

AD软件里间距默认是0.036mm,0.8mm算是20H,50mil=1.27mm,算是35H。

3W原则

场景:50欧姆特性阻抗传输线;

效果:使信号间的串扰减少70%;

应用:时钟线、差分线、视频/音频信号线、复位信号线。

(2)电源平面层叠

如果相邻平面都是电源,要避免铜皮或者走线平行处理,平行的话会产生电势。

图2 弹窗为单个引脚视图_A7

二、PCB阶段

(1)基本原则

20H原则

原因:电源平面和地平面相互耦合RF能量,导致边缘磁通泄露;

期望:抑制边缘辐射效应,提高EMC,使得电场只在gnd层范围内传导;

10H磁通泄露显著改变,20H抑制70%,100H抑制98%;

不知道gnd和power的实际间距,建议内缩50mil;

AD软件里间距默认是0.036mm,0.8mm算是20H,50mil=1.27mm,算是35H。

3W原则

场景:50欧姆特性阻抗传输线;

效果:使信号间的串扰减少70%;

应用:时钟线、差分线、视频/音频信号线、复位信号线。

(2)电源平面层叠

如果相邻平面都是电源,要避免铜皮或者走线平行处理,平行的话会产生电势。

解决方法:错开点,不要重叠;中间加地层;重叠部分变为和上层同一个电源。

(3)载流能力

2.54mm=100mil;

铜线载流能力:表层1oz(35mil的厚度)20mil@1A,内电层0.5oz,40mil@1A;

空间较小时使用8-14/6-12,关键部位多打几个,增大载流能力,注意电流不听话,不是均匀分配的;

过孔通流能力如表1:

表1 过孔通流能力

| 孔内径(mil) |

孔外径(mil) |

设计推荐值(A) |

| 10 |

20 |

1.0 |

|

12

|

24 |

1.2 |

| 16 |

30 |

1.4 |

| 20 |

40 |

1.5 |

(4)规则设置

注意放置过孔的间距,间距最好是保证我们的两个过孔之间最少能够穿过一根线;

设置内电层的保护环7mil;

大丝印:高30mil,宽5mil;小丝印:高15mil,宽3mil,字体serif。

(5)整体布局

电源线距

电源线和信号线间距要超过20mil,这样干扰较少,否则靠近3.3V电源线走一条GND,屏蔽对信号线的干扰;

并行电源线,若压差差距不大,可以距离近些,若差的大可以距离远点,可以以线宽度的2分之一,3分之一,4分之一,5分之一做距离。当然了,条件满足的话,越大越好。

安装孔

安装孔下面的平面层挖空,后期防止螺钉磨损接触到平面层导通;

尽量给安装孔四周留较大空间,至少5mm。

(6)差分走线

遇到阻抗匹配,参考:阻抗匹配设计_ SI9000 学习笔记;

蛇形走线快捷键:TR;

高速线使用arcs(圆弧);

最大幅值 Max Amplitude 3w(差分等长要 gap>=4w);

调节快捷键:幅度 < ,gap间隔 3/4 ,弧度 1/2(字母上边的数字,不是小键盘);

若连线分段了,不是一条完整的线,则只能在每一段上分别走TR,或者重新连一下,一下走完。

(7)敷铜

电气

信号完整性要求,给高频数字信号一个完整的回流路径,并减少直流网络的布线;

数字电路中存在大量尖峰脉冲电流,而地网络的干扰能量U=I*R,因此降低地线阻抗尤为重要。所谓抗干扰有很大一部分是通过降低地线阻抗实现的,因此大量的铺铜或者完整的地平面能够降低地线阻抗,从而增强系统的抗干扰能力;

对于电源来说,其传输路径包括电源路径和回流路径地,整个传输路径的压降U=I*R,该路径上的直流电阻R越低,压降就越低。因此大量的铺铜能够降低电源传输路径上的直流电阻,减小电源回路面积,从而降低其压降,提高电源的传输效率;

铺不铺:如果表层器件、布线较多, 很难保证铜箔完整,还会带来内层信号跨分割问题,那就放弃铺铜。

EMC

对于大面积的地或电源铺铜,会起到屏蔽作用,有些特殊地,如屏蔽层地PGND起到防护作用;

铺不铺:上下两层表面铺地对EMC有好处,但是铺铜要尽量完整,避免出现孤岛。所以,如果不完整、离散大,那就放弃铺铜。

散热

特殊器件安装要求铺铜增加散热,主芯片、电源下边一般要有几层的铺铜。

工艺

为了保证电镀效果、或层压不变形,在走线层空白地方也是要进行铺铜;

大部分是用实心铜的 ,屏蔽性方面也比较好,网格铜一般常见在FPC软板上面。

(8)快捷键(Altium Designer)

多根走线:TTM或者PM

蛇形走线:TR

栅格步进大小(移动元器件精度):ctrl+g

丝印整体位置调整:AP

(9)后期检查

PCB检查连线接触不良,线宽0.1mil,过孔4-6mil;

3D视角查看平面层、敷铜、安装孔破坏铜皮处,是否存在尖角,防止天线效应;

丝印标明二极管、LED正负端,可以约定丝印靠近端即为正极;

最好做自己风格的一张checklist。

∑ 后期学习中若遇到其他的重点、注意点,会不断积累补充~

作者:CrazyFPGA

pcb