计算机组成原理 第四章 存储系统(1)

文章目录4.1 存储系统层次结构1.基本存储体系2.主存速度慢的原因3.主存容量不足的原因4.存储体系的层次化结构5.存储体系层次化结构的理论基础4.2 主存中的数据组织1.存储字长2.数据存储和边界的关系3.大端与小端存储方式4.3 静态存储器工作原理1.SRAM存储单元结构2.SRAM存储单元工作原理3.静态存储器的结构4.4 动态存储器工作原理1.SRAM存储单元的不足2.DRAM存储单元的基本结构3.DRAM存储单元的工作原理4.DRAM存储单元的刷新5.DRAM与SRAM的对比6.其他结构的DRAM存储单元4.5 存储扩展1.存储扩展的基本概念及类型2.位扩展举例3.字扩展举例4.字位同时扩展

4.1 存储系统层次结构

1.基本存储体系

输入设备将程序与数据写入主存;

CPU取指令;

CPU执行指令期间读数据;

CPU写回运算结果;

输出设备输出结果;

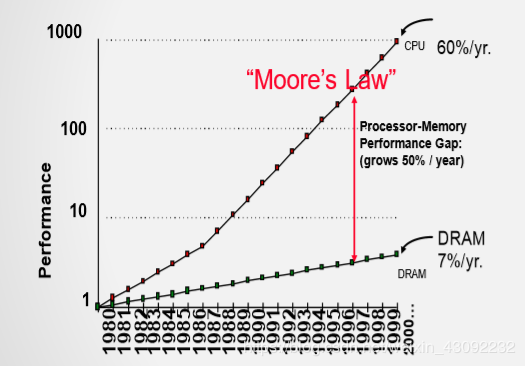

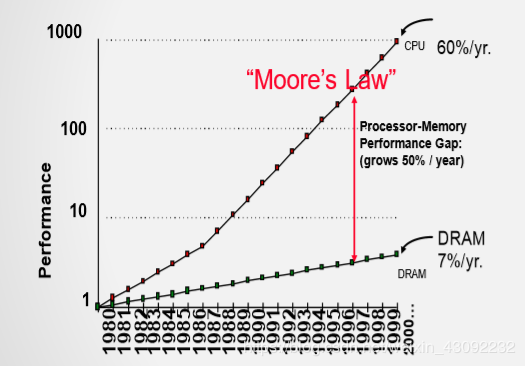

2.主存速度慢的原因

主存增速与CPU不同步;

指令执行期间多次访问存储器;

3.主存容量不足的原因

存在制约主板容量的技术因素 由CPU、主板等相关技术指标确定

3.主存容量不足的原因

存在制约主板容量的技术因素 由CPU、主板等相关技术指标确定

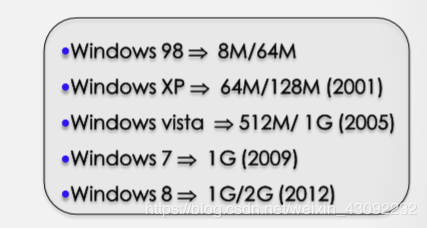

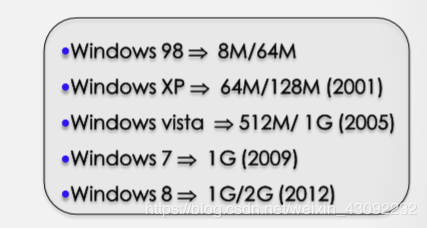

应用对主存的需求不断扩大

应用对主存的需求不断扩大

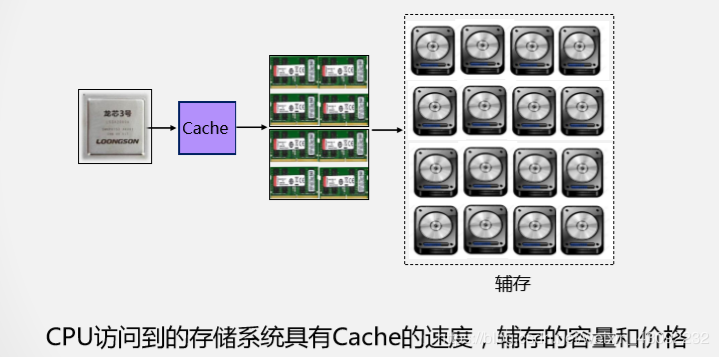

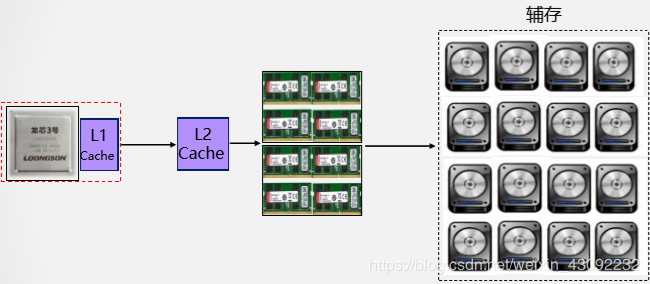

4.存储体系的层次化结构

4.存储体系的层次化结构

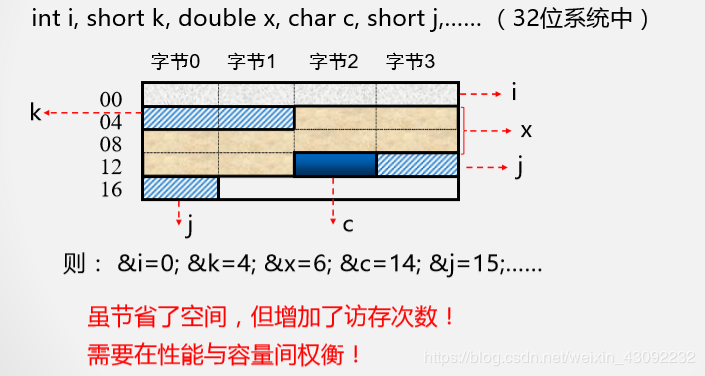

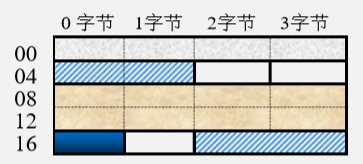

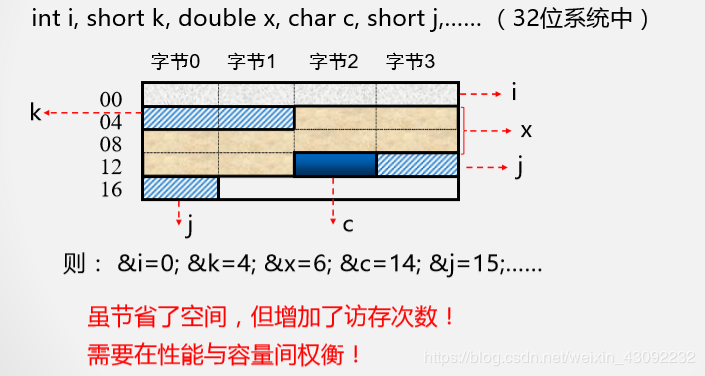

未按边界对齐的数据存储

未按边界对齐的数据存储

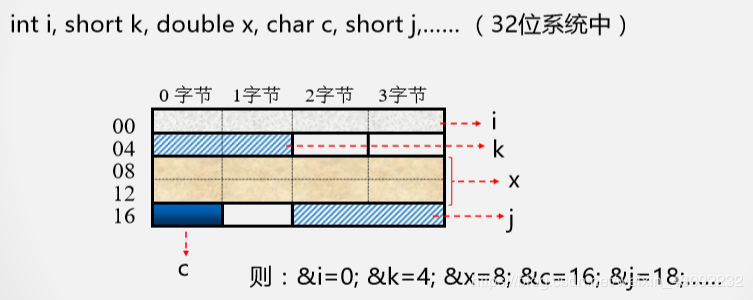

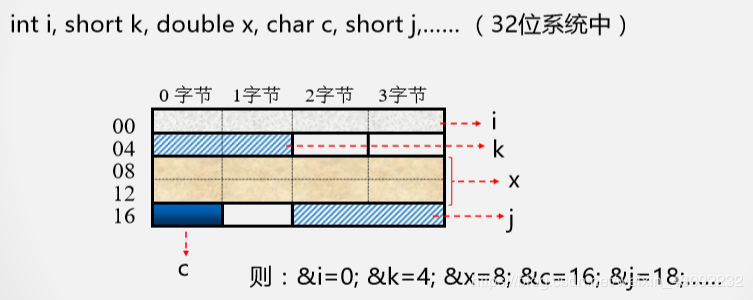

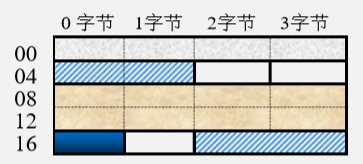

边界对齐与存储地址的关系(以32位为例)

边界对齐与存储地址的关系(以32位为例)

双字长数据边界对齐的起始地址的最末三位为000(8字节整数倍);

单子长边界对齐的起始地址的末二位为00(4字节整数倍);

半字长边界对齐的起始地址的最末一位为0(2字节整数倍)

双字长数据边界对齐的起始地址的最末三位为000(8字节整数倍);

单子长边界对齐的起始地址的末二位为00(4字节整数倍);

半字长边界对齐的起始地址的最末一位为0(2字节整数倍)

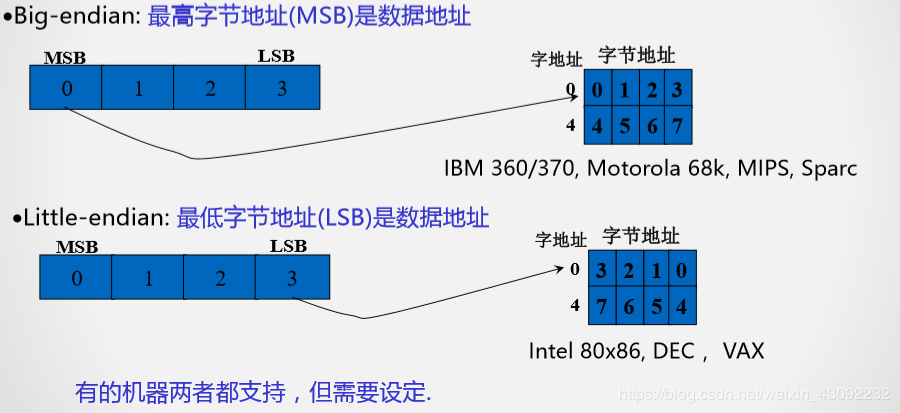

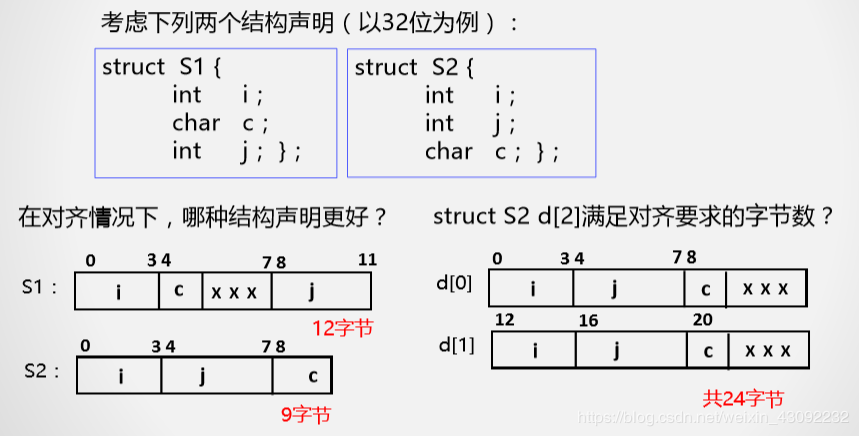

即高字节对应低地址,低字节对应高地址 Little-endian:最低字节地址(LSB)是数据地址

即低字节对应低地址,高字节对应高地址

举例而言:数字0x12 34 56 78在内存中储存

作者:Wo_Knight

3.主存容量不足的原因

存在制约主板容量的技术因素 由CPU、主板等相关技术指标确定

3.主存容量不足的原因

存在制约主板容量的技术因素 由CPU、主板等相关技术指标确定 应用对主存的需求不断扩大

应用对主存的需求不断扩大 4.存储体系的层次化结构

4.存储体系的层次化结构

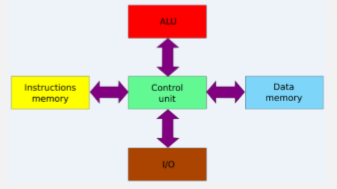

哈佛结构(Harvard architecture)

局部性原理

时间局部性

现在被访问的信息2在不久的将来还将再次被访问 时间局部性的程序结构体现:循环结构空间局部性

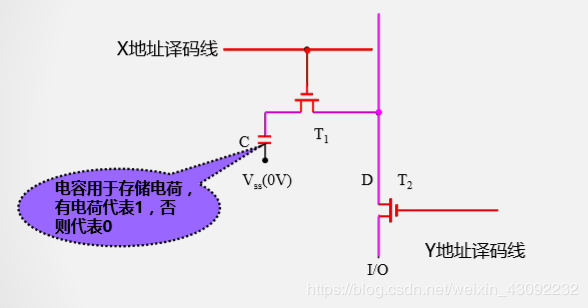

现访问信息2,下一次访问2附近的信息 空间局部性的程序结构体现:顺序结构 4.2 主存中的数据组织 1.存储字长 主存的一个存储单元所包含的二进制位数; 目前大多数计算机的主存按字节编址,存储字长也不断加大,如16位字长、32位字长和64位字长; 2.数据存储和边界的关系 按边界对齐的数据存储 未按边界对齐的数据存储

未按边界对齐的数据存储 边界对齐与存储地址的关系(以32位为例)

边界对齐与存储地址的关系(以32位为例) 双字长数据边界对齐的起始地址的最末三位为000(8字节整数倍);

单子长边界对齐的起始地址的末二位为00(4字节整数倍);

半字长边界对齐的起始地址的最末一位为0(2字节整数倍)

双字长数据边界对齐的起始地址的最末三位为000(8字节整数倍);

单子长边界对齐的起始地址的末二位为00(4字节整数倍);

半字长边界对齐的起始地址的最末一位为0(2字节整数倍)

大端与小端模式详解

Big-endian:最高字节地址(MSB)是数据地址即高字节对应低地址,低字节对应高地址 Little-endian:最低字节地址(LSB)是数据地址

即低字节对应低地址,高字节对应高地址

举例而言:数字0x12 34 56 78在内存中储存

大端模式下:

低地址----------->高地址

0x12 | 0x34 | 0x56 | 0x78

小端模式下:

低地址----------->高地址

0x78 | 0x56 | 0x34 | 0x12

4.3 静态存储器工作原理

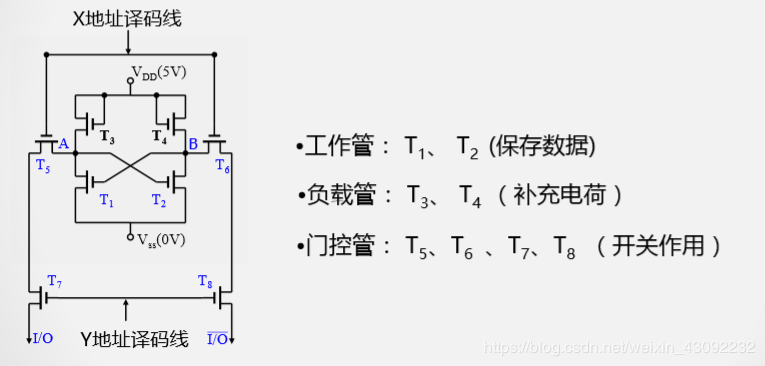

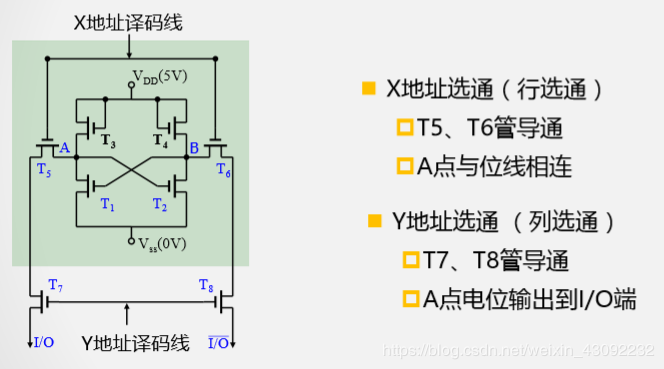

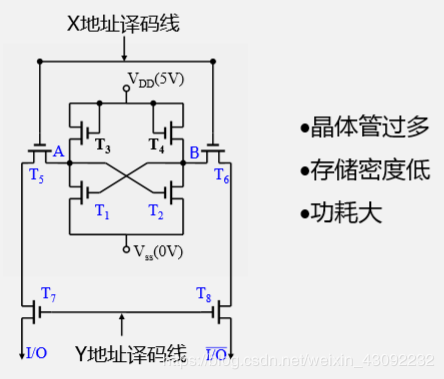

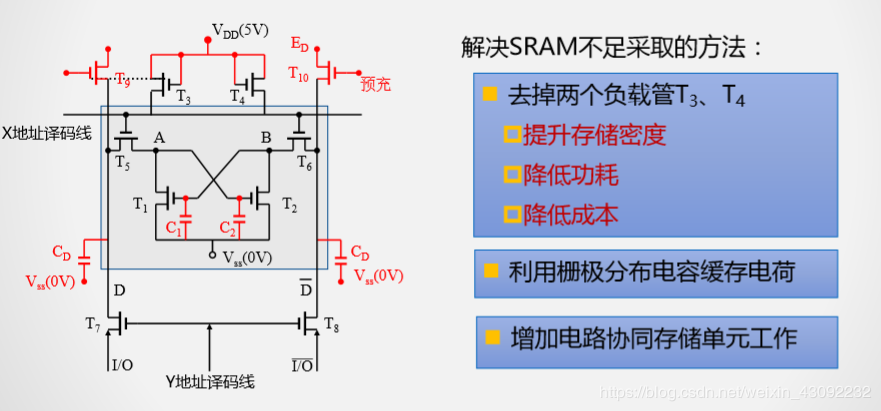

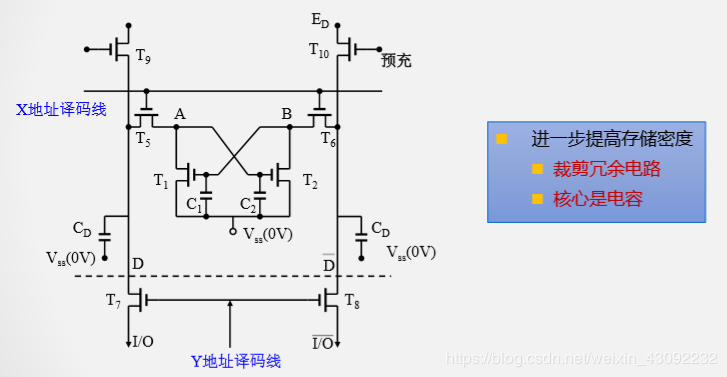

1.SRAM存储单元结构

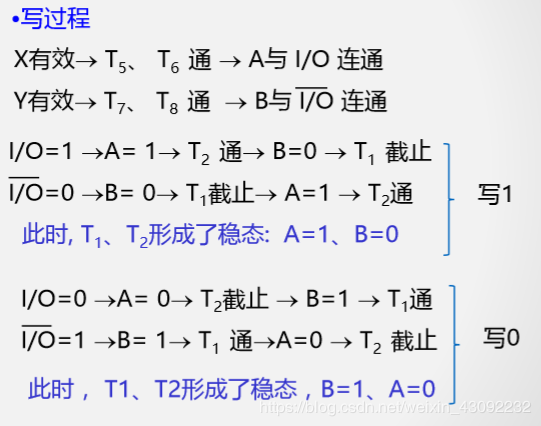

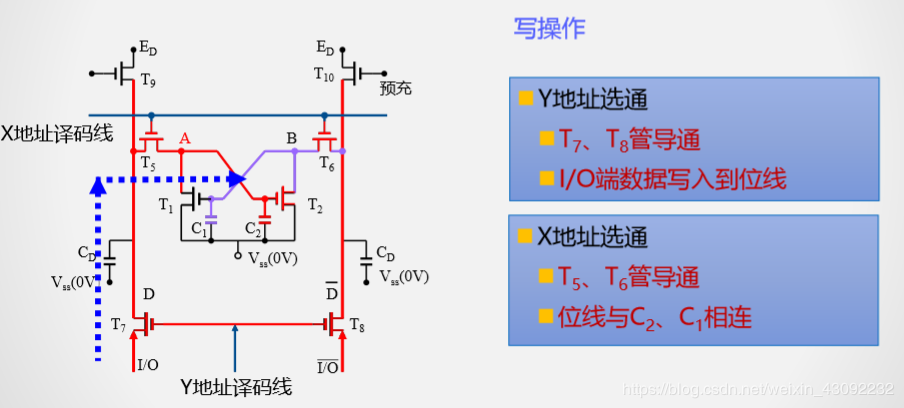

写过程

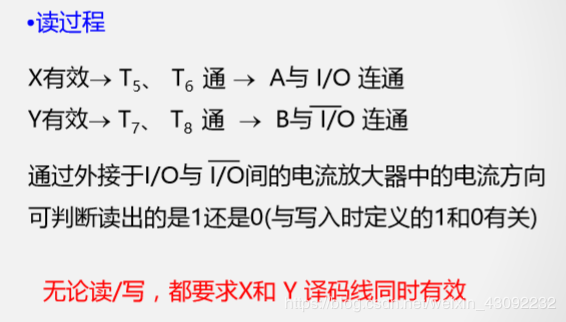

读过程

保持

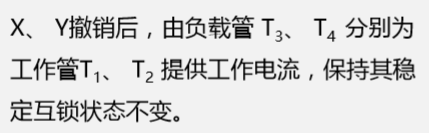

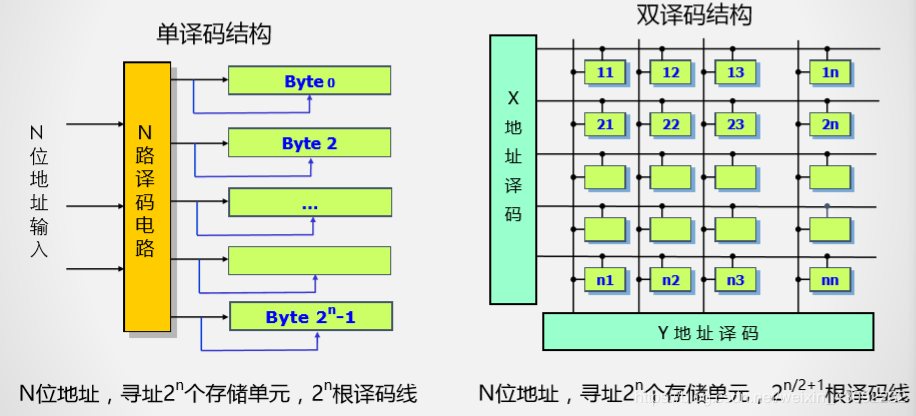

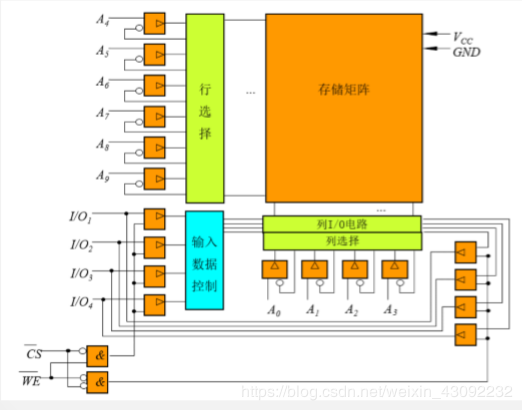

静态存储器分为单译码结构和双译码结构

6116静态存储器结构

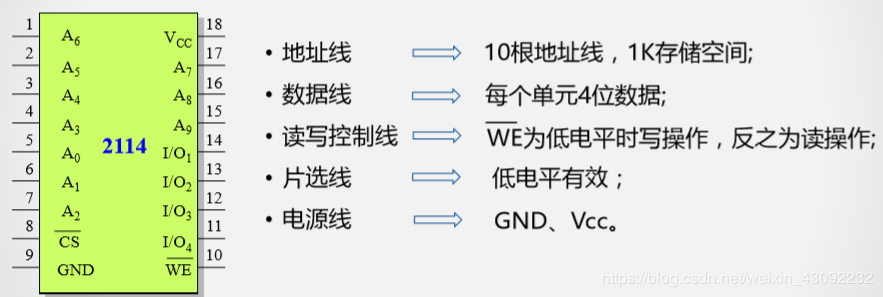

2114静态存储器结构

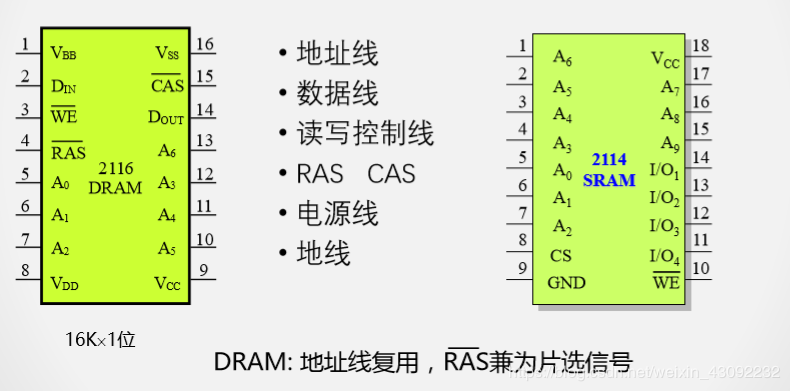

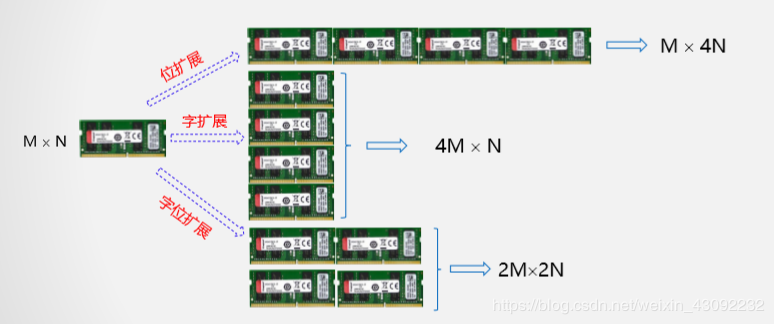

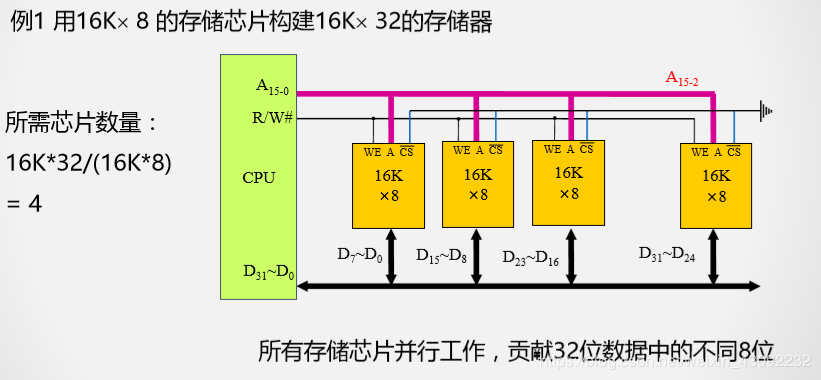

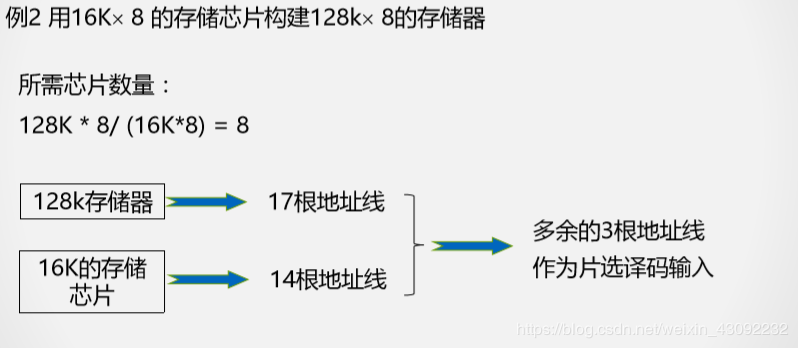

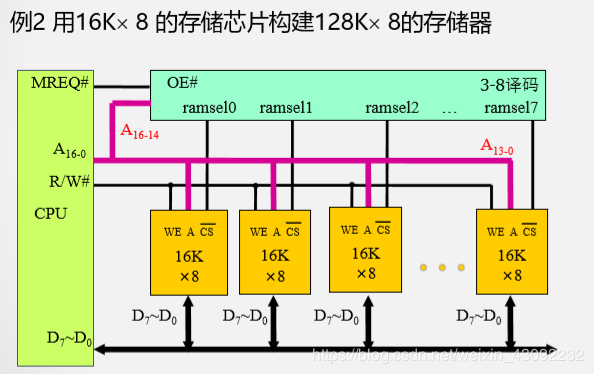

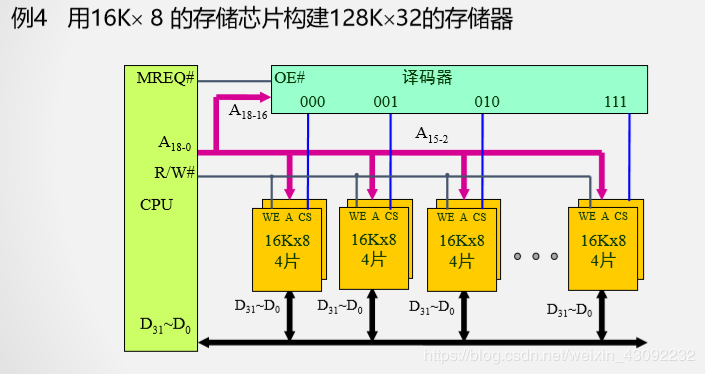

存储扩展包括 位扩展、字扩展、字位扩展,无论哪种类型的存储扩展都要完成CPU与主存间地址线、数据线、控制线的连接

作者:Wo_Knight