AXI总线——工作原理

AXI总线

一.AXI总线通道

(1)读地址通道,包含ARVALID, ARADDR, ARREADY信号;主机->从机

(2)写地址通道,包含AWVALID,AWADDR, AWREADY信号;主机->从机

(3)读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;从机->主机

(4)写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;主机->从机

(5)写应答通道,包含BVALID, BRESP, BREADY信号;从机->主机

另外:还有两个global signal,ACLK,ARESETN信号,其中ACLK为AXI总线时钟信号,ARESETN为AXI总线复位信号;

READY与VALID是对应的通道握手信号;WSTRB:数据段有效(标记写数据中哪几个8位字段有效);WSTRB信号为1的bit对应WDATA有效数据字节,WSTRB宽度是32bit/8=4bit;BRESP与RRESP分别为写回应信号,读回应信号;

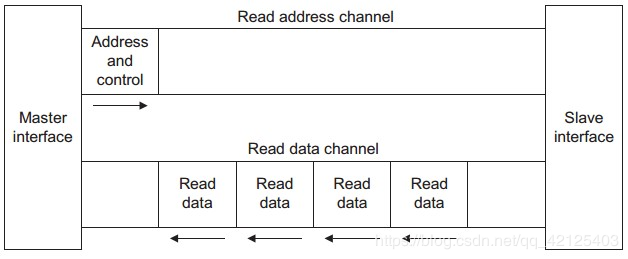

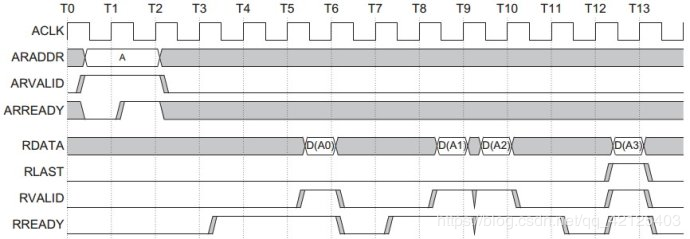

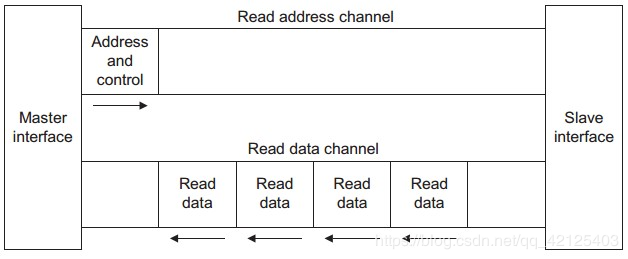

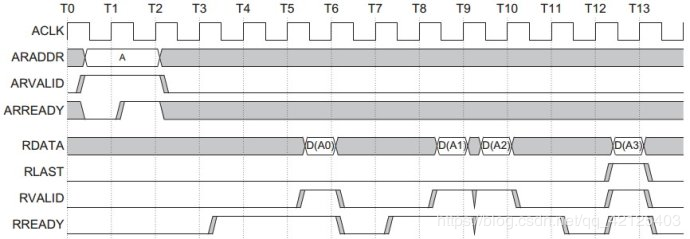

1>读操作

主与从进行读地址通道握手并传输地址内容;

读数据通道握手并传输所读内容以及读取操作的回应;

对于读操作,slave必须先知道master想要读取的地址,因此,slave必须先接收到command后再回数据。操作如图所示:

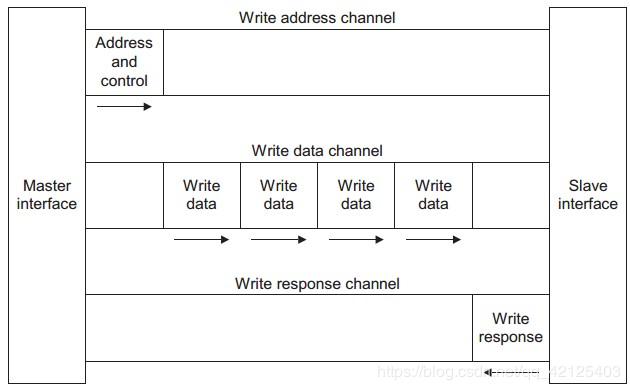

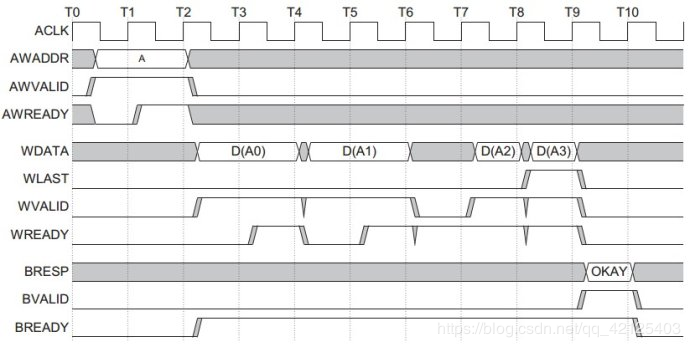

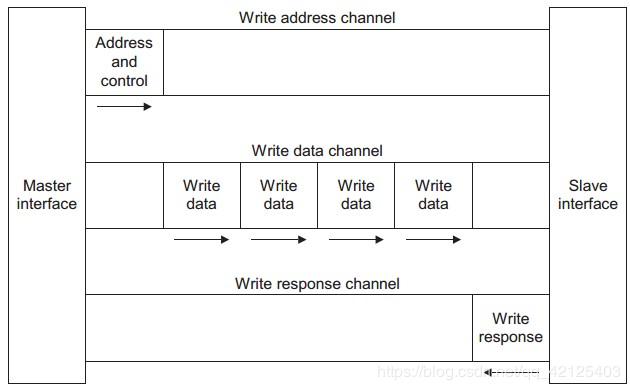

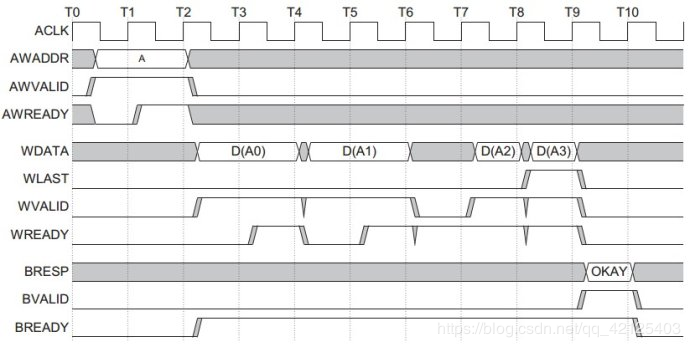

2>写操作

主与从进行写地址通道握手并传输地址内容;

写数据通道握手并传输所读内容;

写回应通道握手,并传输写回应数据;

对于写操作,command和数据都是master发给slave的,因此command和data没有顺序,可以先发command,再发data,也可以先发data,在发送data过程中发送command。操作如图所示:

2>写操作

主与从进行写地址通道握手并传输地址内容;

写数据通道握手并传输所读内容;

写回应通道握手,并传输写回应数据;

对于写操作,command和数据都是master发给slave的,因此command和data没有顺序,可以先发command,再发data,也可以先发data,在发送data过程中发送command。操作如图所示:

作者:小白-accelerator

作者:小白-accelerator

2>写操作

主与从进行写地址通道握手并传输地址内容;

写数据通道握手并传输所读内容;

写回应通道握手,并传输写回应数据;

对于写操作,command和数据都是master发给slave的,因此command和data没有顺序,可以先发command,再发data,也可以先发data,在发送data过程中发送command。操作如图所示:

2>写操作

主与从进行写地址通道握手并传输地址内容;

写数据通道握手并传输所读内容;

写回应通道握手,并传输写回应数据;

对于写操作,command和数据都是master发给slave的,因此command和data没有顺序,可以先发command,再发data,也可以先发data,在发送data过程中发送command。操作如图所示:

作者:小白-accelerator

作者:小白-accelerator