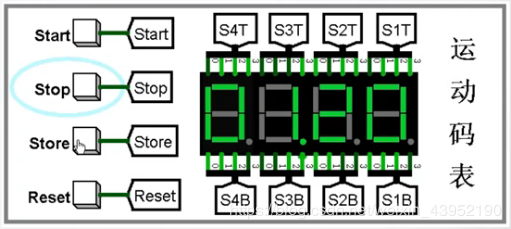

小型数字系统---运动码表

熟悉数字系统基本特征及设计方法,熟练掌握数字系统设计基本流程,利用Logisim构建运动码表数据通路和控制逻辑,最终完成整个码表功能的设计。

二,实验内容设计电路并使用Logisim软件进行虚拟仿真,具体内容及要求如下:

输入:4个按钮。

输出:4个7段数码管显示数字。

具体功能:

(1)当按下Start时,计时器清零,重新开始计时;

(2)当按下Stop时,计时器停止计时,显示计时数据;

(3)当按下Store时,若当前计时数据小于系统记录,则更新系统记录,并显示当前计时数据;否则不更新系统记录,但显示系统记录。

(4)当按下Reset时,复位,计时=0.00, 系统记录=99.99。

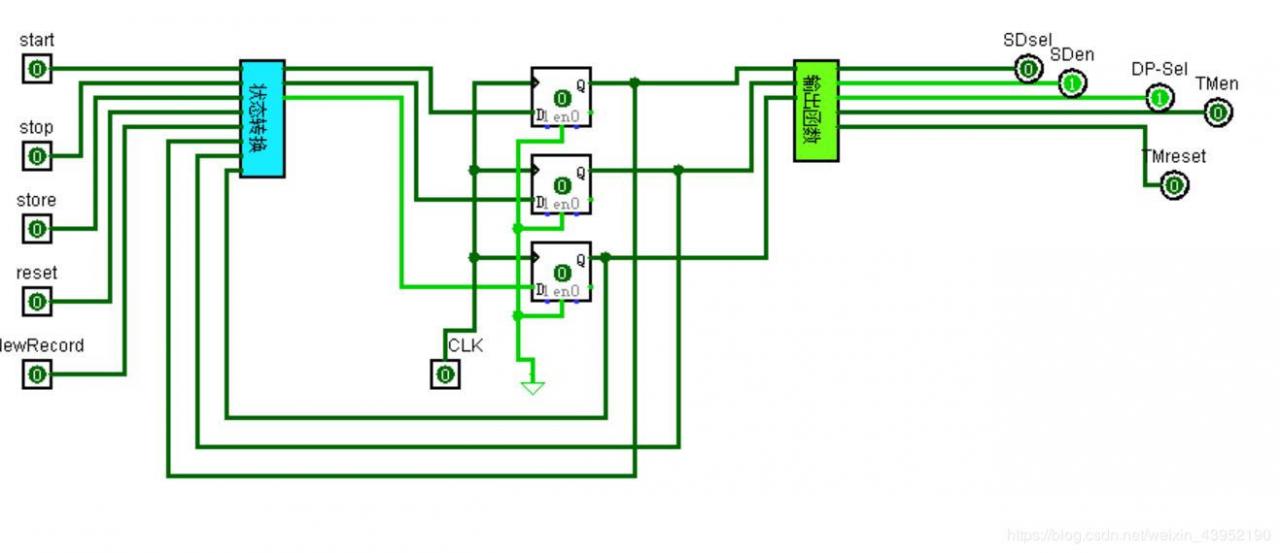

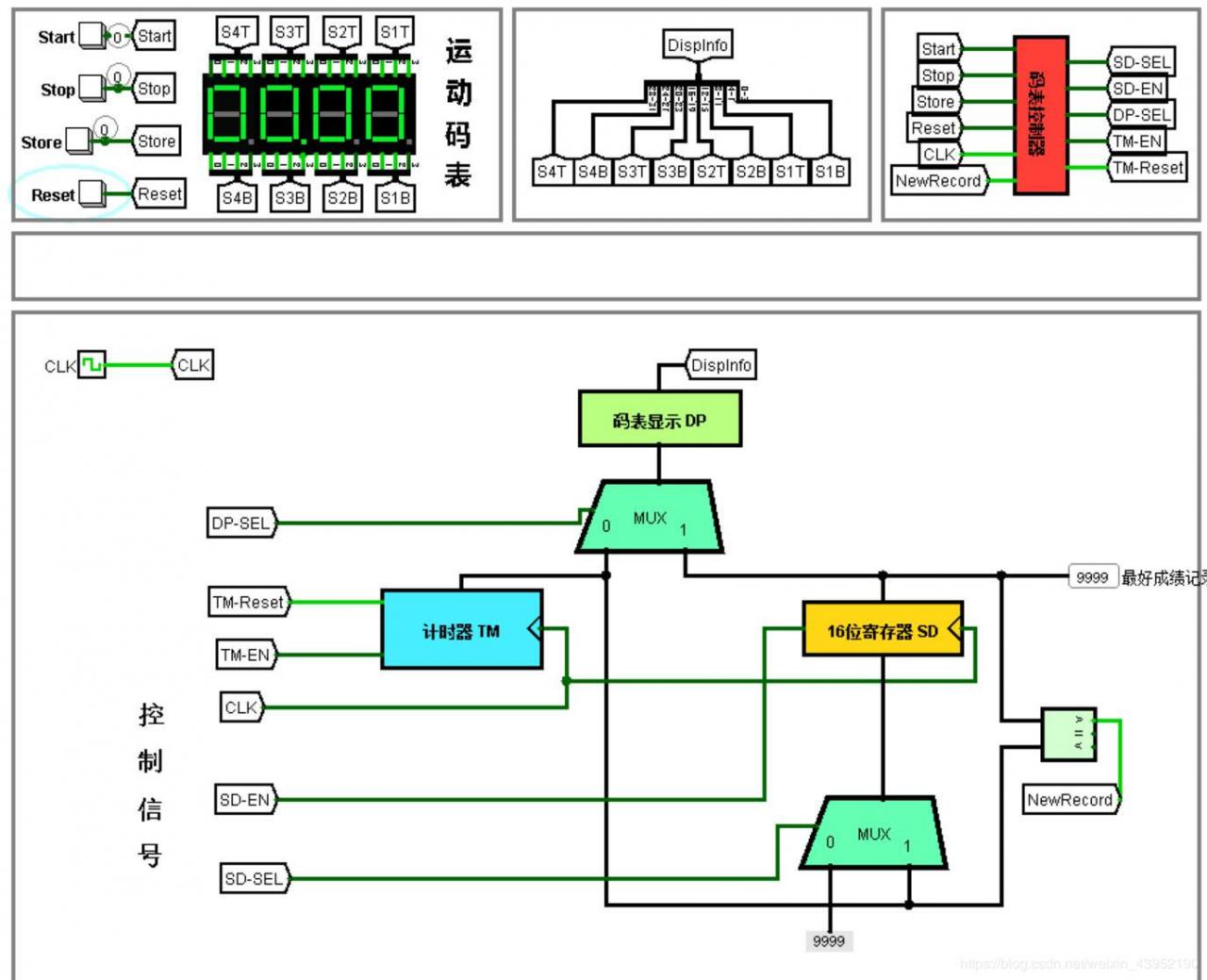

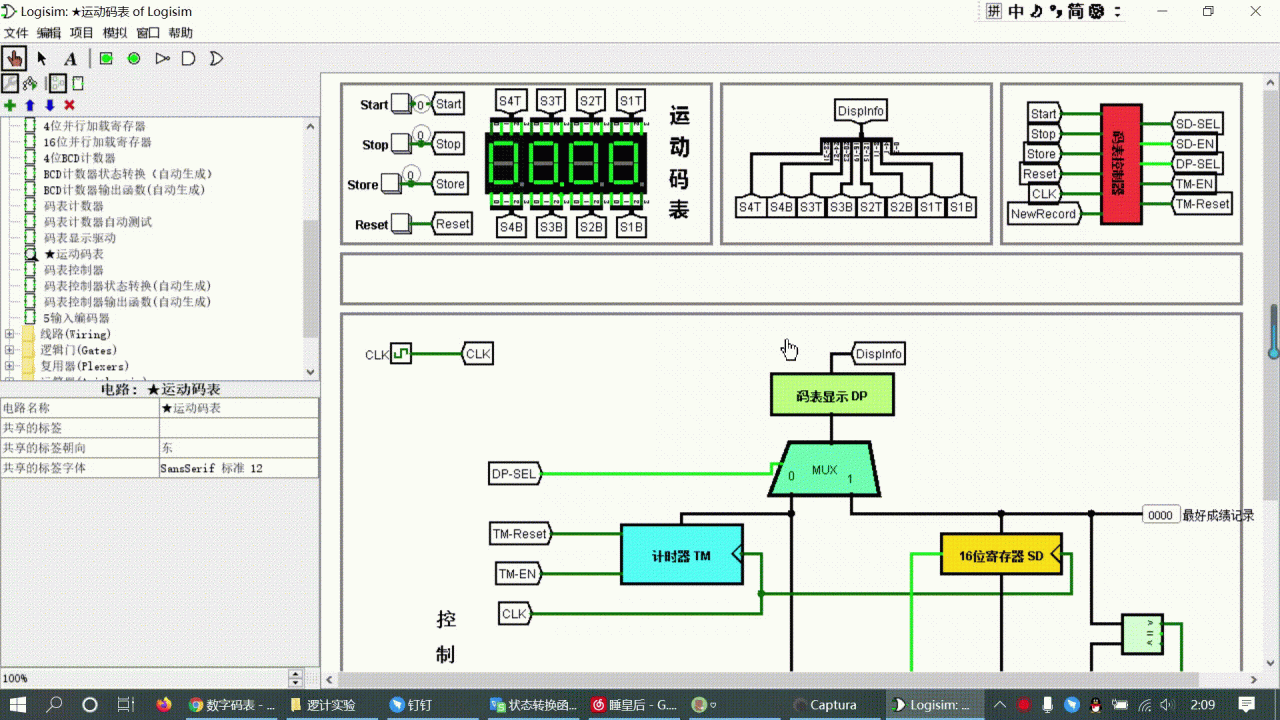

1)设计码表功能部件,如计数器、16位寄存器、数码管显示、比较器、2路选择器等,可使用之前实验的电路封装。各功能部件的控制信号及输入输出如下表。TM-En和TM-Rst分别为计时器使能端和清零端(复位端)。SD-En为寄存器使能端。

2)构建功能部件之间的数据通路,明确功能部件之间的输入、输出和具体连线。其中主要功能部件的数据输入和数据来源如下表。TM.Q和SD.Q分别为计时器输出和寄存器输出。SD-sel和DP-Sel为选择控制信号。NewRecord为根据比较器的比较结果产生的状态信号,可以反馈给控制器作为输入。

设计码表控制器

这里便用到了数电中“时序电路设计”的知识,时序电路中的组合逻辑部分,可拆分为“状态转换电路”和“输出转换电路”两部分。

| 状态 | 编码 | 功能 |

|---|---|---|

| 复位 | 000 | 清除寄存器记录,默认恢复9999 |

| 清零 | 001 | 计时器复位 |

| 计数 | 011 | 计时器计数 |

| 暂停 | 010 | 暂停计时 |

| 存储 | 110 | 寄存器存入新数据 |

| 显示 | 100 | 显示寄存器中的内容 |

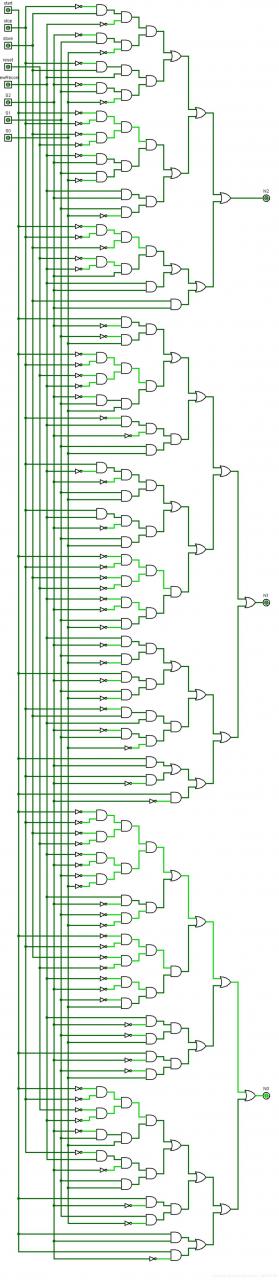

画出各个对应的状态转换图,输入excel中生成逻辑表达式,自动生成电路图:

然后进行生成输出函数

| 状态 | 编码 | 控制输出 |

|---|---|---|

| 复位 | 000 | DP-Sel=1,SDEN=1 |

| 清零 | 001 | TM-RESET=1 |

| 计数 | 011 | TM-EN=1 |

| 暂停 | 010 | 全部为0 |

| 存储 | 110 | SPSEL=1,SDEN=1,DP-SEL=1 |

| 显示 | 100 | SD-SEL=1,DPSEL=1 |

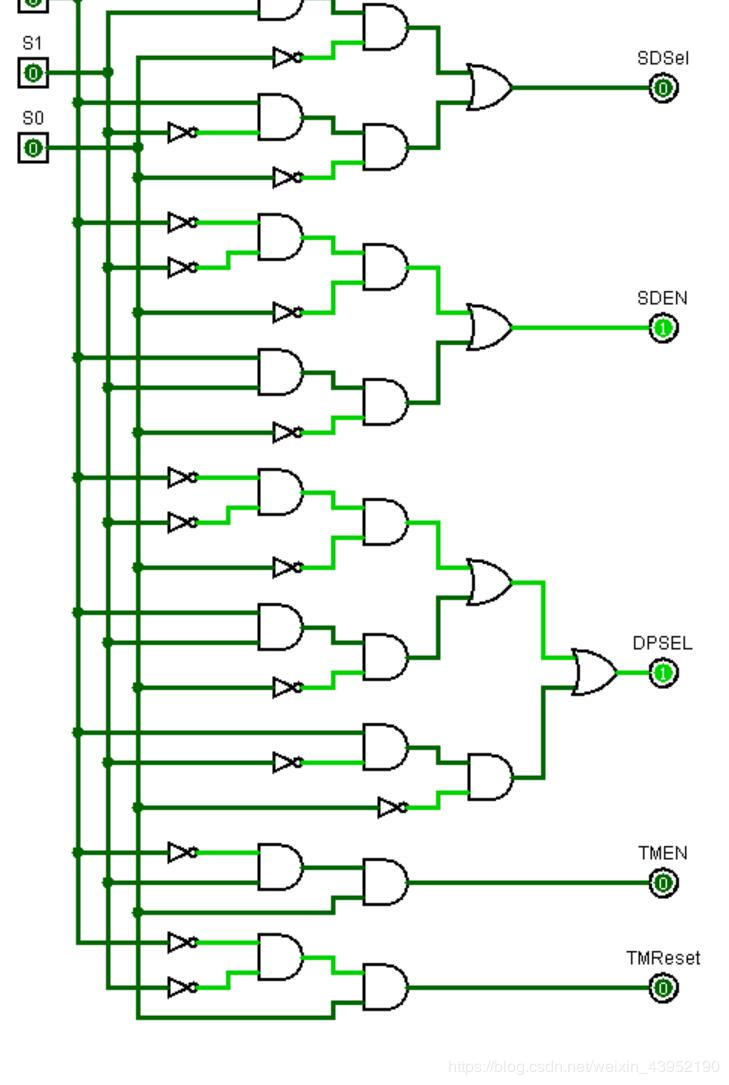

3)构建码表控制器,明确码表使用中的状态数,构建状态图,再构建状态转换表和输出函数逻辑。其中外部控制输入信号包括Start, Stop, Reset, Store,内部控制信号为TM-EN, TM-Reset, SD-EN, SD-SEL, DP-SEL。NewRecord为状态输出信号。

码表控制线路

最终,运动码表的总线路

作者:marsxu626