【VHDL设计—数字传输系统】ASK调制与FSK调制

文章目录

仿真操作指导“手册”

1、ASK调制(键控法实现)

2、FSK调制(键控法实现)

3、FSK调制(Mini模拟实现法)

本次工程文件夹(压缩包)下载

仿真操作指导“手册”☞☞【VHDL设计—数字系统验证】最新Testbench仿真教程(包含Testbench设计的基础知识、仿真操作步骤、问题集绵)

1、ASK调制(键控法实现) ASK_modulate.v

module ASK_modulate(clk, start, x, y);

input clk;

input start; //开始调制的信号

input x; //基带信号(调制前的信号)

output y; //调制后的信号

wire y=0;

reg [1:0] q; //分频计数器

reg f; //载波信号

always @(posedge clk)

begin

if(start == 0)

q <= 0 ;

else if(q <= 1) //

begin

f <= 1;

q <= q + 1;

end

else if(q==3) //

begin

f <= 0;

q <= 0;

end

else //

begin

f <= 0;

q <= q + 1;

end

end

assign y = x && f; //对基带信号进行调制

endmodule

TB_ASK_Modulate.v (testbench仿真程序)

`timescale 100ns/1ps //延时间隔单位为0.1us

module TB_ASK_Modulate();

reg CLK, START, X;

//parameter initTime = 30;

parameter period = 2;

ASK_modulate Obj(.clk(CLK), .start(START), .x(X));

/*时钟脉冲信号,占空比为50%,周期为period=0.2us*/

initial

begin

CLK = 0;

//#initTime;

forever

#(period/2) CLK = ~CLK;

end

/*同步启动信号,CLK的第一个下降沿到来后开始ASK调制*/

initial

begin

START=0;

@(posedge CLK);

START=1;

end

/*基带信号*/

initial

begin

X=0;

#50 X=1; // 1持续5us

#50 X=0; // 0持续5us

#50 X=1; // 1持续10us

#100 X=0; // 0持续10us

#100 X=1; // 1持续5us

#50 X=0; // 0持续10us

#100 X=1; // 1持续5us

#50 X=0; // 0持续不变

end

endmodule

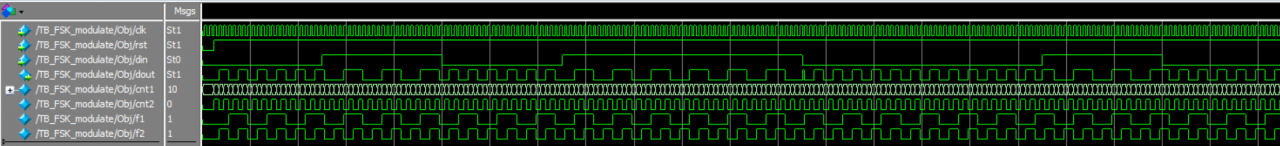

仿真结果

2、FSK调制(键控法实现)

FSK_modulate.v

module FSK_modulate(clk, rst, din, dout);

input clk , rst ;

input din;

output dout;

reg [1:0] cnt1;

reg cnt2;

reg f1,f2;

always @(posedge clk or negedge rst)

begin

if(rst==0)

begin

cnt1 <= 2'b00;

f1 <= 0;

end

else if(cnt1 == 2'b11)

begin

cnt1 <= 2'b00;

f1 <= ~f1;

end

else

cnt1 <= cnt1 +1;

end

always @(posedge clk or negedge rst)

begin

if(rst==0)

begin

cnt2 <= 2'b00;

f2 <= 0;

end

else if(cnt2 == 2'b01)

begin

cnt2 <= 2'b00;

f2 <= ~f2;

end

else

cnt2 <= cnt2 +1;

end

assign dout =(din==1)?f1:f2;

endmodule

TB_FSK_modulate.v (testbench仿真程序)

`timescale 100ns/1ps //延时间隔为0.1us

module TB_FSK_modulate();

reg CLK, RST, DIN;

parameter period = 2;

FSK_modulate Obj(.clk(CLK), .rst(RST), .din(DIN));

/*时钟脉冲信号,占空比为50%,周期为period=0.2us*/

initial

begin

CLK = 0;

forever

#(period/2) CLK = ~CLK;

end

/*异步复位,0.5us后开始复位*/

initial

begin

RST=0;

#5;

RST=1;

end

/*基带信号*/

initial

begin

DIN=0;

#50 DIN=~DIN; // 1持续5us

#50 DIN=~DIN; // 0持续5us

#50 DIN=~DIN; // 1持续10us

#100 DIN=~DIN; // 0持续10us

#100 DIN=~DIN; // 1持续5us

#50 DIN=~DIN; // 0持续10us

#100 DIN=~DIN; // 1持续5us

#50 DIN=0; // 0持续不变

end

endmodule

仿真结果

3、FSK调制(Mini模拟实现法)

FSK_modulate_mini.v

module FSK_modulate_mini(

input clk,//时钟信号

output reg [7:0]sigOut,//输出已调信号

output reg [7:0]carryWave1,//1对应的载波幅度

output reg [7:0]carryWave0,//0对应的载波幅度

output wire codeSource,//数字基带信号

output reg codeClk=0,//用来控制数字基带信号的时钟

output reg stClk=0//用来控制载波的时钟,数字基带时钟周期应为载波时钟的n倍

);

//分频器部分

reg [7:0]codeClkCount=0;//时钟计数器

reg [3:0]carryClkCount=0;//载波时钟计数器

always @(posedge clk)

begin

//codeClk

if(codeClkCount==127)

begin

codeClk=~codeClk;

codeClkCount=0;

end

else

begin

codeClkCount=codeClkCount+1;

end

//carryClk

if(carryClkCount==1)

begin

stClk=~stClk;

carryClkCount=0;

end

else

begin

carryClkCount=carryClkCount+1;

end

end

//数字基带信号,m序列发生器

reg [5:0]outReg=6'b010101;//序列寄存器初始化

reg mAdded;//m序列移位的辅助变量

assign codeSource=outReg[5];//输出变量为寄存器序列的最高位

always @(negedge codeClk)

begin

//手动异或

if(outReg[0]==outReg[5])

begin

mAdded=0;

end

else

begin

mAdded=1;

end

outReg=outReg<<1;//对寄存器左移

outReg=outReg+mAdded;

end

//载波的产生

reg [7:0]waveCount=0;//载波幅度查询变量

always @(posedge stClk)

begin

if(waveCount==63)

begin

waveCount=0;

end

else

begin

waveCount=waveCount+1;

end

//根据查询变量进行载波幅度查询

case(waveCount)

0: begin carryWave0<=0;carryWave1<=0; end

1: begin carryWave0<=12;carryWave1<=25; end

2: begin carryWave0<=25;carryWave1<=49; end

3: begin carryWave0<=37;carryWave1<=71; end

4: begin carryWave0<=49;carryWave1<=90; end

5: begin carryWave0<=60;carryWave1<=106; end

6: begin carryWave0<=71;carryWave1<=117; end

7: begin carryWave0<=81;carryWave1<=125; end

8: begin carryWave0<=90;carryWave1<=127; end

9: begin carryWave0<=98;carryWave1<=125; end

10:begin carryWave0<=106;carryWave1<=117; end

11:begin carryWave0<=112;carryWave1<=106; end

12:begin carryWave0<=117;carryWave1<=90; end

13:begin carryWave0<=122;carryWave1<=71; end

14:begin carryWave0<=125;carryWave1<=49; end

15:begin carryWave0<=126;carryWave1<=25; end

16:begin carryWave0<=127;carryWave1<=0; end

17:begin carryWave0<=126;carryWave1<=-25; end

18:begin carryWave0<=125;carryWave1<=-49; end

19:begin carryWave0<=122;carryWave1<=-71; end

20:begin carryWave0<=117;carryWave1<=-90; end

21:begin carryWave0<=112;carryWave1<=-106; end

22:begin carryWave0<=106;carryWave1<=-117; end

23:begin carryWave0<=98;carryWave1<=-125; end

24:begin carryWave0<=90;carryWave1<=-127; end

25:begin carryWave0<=81;carryWave1<=-125; end

26:begin carryWave0<=71;carryWave1<=-117; end

27:begin carryWave0<=60;carryWave1<=-106; end

28:begin carryWave0<=49;carryWave1<=-90; end

29:begin carryWave0<=37;carryWave1<=-71; end

30:begin carryWave0<=25;carryWave1<=-49; end

31:begin carryWave0<=12;carryWave1<=-25; end

32:begin carryWave0<=0;carryWave1<=0; end

33:begin carryWave0<=-12;carryWave1<=25; end

34:begin carryWave0<=-25;carryWave1<=49; end

35:begin carryWave0<=-37;carryWave1<=71; end

36:begin carryWave0<=-49;carryWave1<=90; end

37:begin carryWave0<=-60;carryWave1<=106; end

38:begin carryWave0<=-71;carryWave1<=117; end

39:begin carryWave0<=-81;carryWave1<=125; end

40:begin carryWave0<=-90;carryWave1<=127; end

41:begin carryWave0<=-98;carryWave1<=125; end

42:begin carryWave0<=-106;carryWave1<=117; end

43:begin carryWave0<=-112;carryWave1<=106; end

44:begin carryWave0<=-117;carryWave1<=90; end

45:begin carryWave0<=-122;carryWave1<=71; end

46:begin carryWave0<=-125;carryWave1<=49; end

47:begin carryWave0<=-126;carryWave1<=25; end

48:begin carryWave0<=-127;carryWave1<=0; end

49:begin carryWave0<=-126;carryWave1<=-25; end

50:begin carryWave0<=-125;carryWave1<=-49; end

51:begin carryWave0<=-122;carryWave1<=-71; end

52:begin carryWave0<=-117;carryWave1<=-90; end

53:begin carryWave0<=-112;carryWave1<=-106; end

54:begin carryWave0<=-106;carryWave1<=-117; end

55:begin carryWave0<=-98;carryWave1<=-125; end

56:begin carryWave0<=-90;carryWave1<=-127; end

57:begin carryWave0<=-81;carryWave1<=-125; end

58:begin carryWave0<=-71;carryWave1<=-117; end

59:begin carryWave0<=-60;carryWave1<=-106; end

60:begin carryWave0<=-49;carryWave1<=-90; end

61:begin carryWave0<=-37;carryWave1<=-71; end

62:begin carryWave0<=-25;carryWave1<=-49; end

63:begin carryWave0<=-12;carryWave1<=-25; end

endcase

end

//调制部分

always @(posedge stClk)

begin

if(codeSource)

begin

sigOut=carryWave1;

end

else

begin

sigOut=carryWave0;

end

end

endmodule

FSK_modulate_mini.v(testbench仿真程序)

`timescale 10ns/10ps

module TB_FSK_modulate_mini();

reg clk;

wire [7:0]sigOut;

wire [7:0]carryWave0;

wire [7:0]carryWave1;

wire codeSource;

wire codeClk;

wire stClk;

FSK_modulate_mini Obj(

.clk (clk),

.sigOut (sigOut),

.carryWave0 (carryWave0),

.carryWave1 (carryWave1),

.codeSource (codeSource),

.codeClk (codeClk),

.stClk (stClk)

);

parameter clkper=100;

initial

begin

clk = 1'b0;

end

always

begin

#(clkper / 2) clk=~clk;

end

endmodule

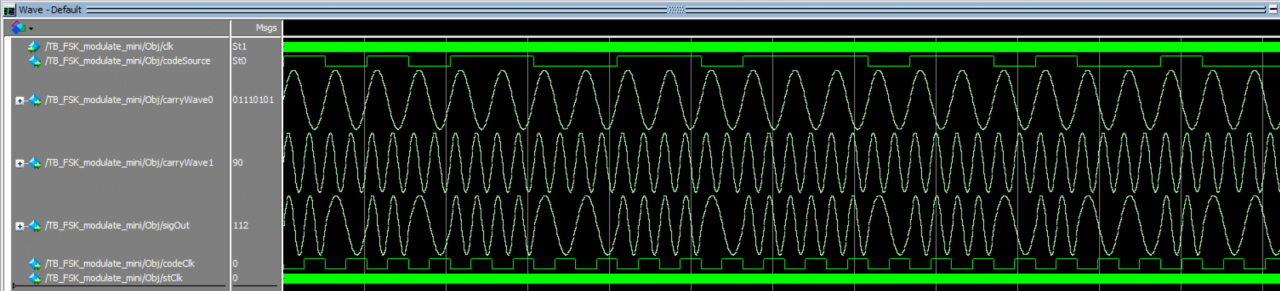

仿真结果

本次工程文件夹(压缩包)下载

ASK调制(键控法实现)

FSK调制(键控法实现)

FSK调制(Mini模拟实现法)

如遇到问题,可在评论区下回复或者私信我哦!我会尽快回复的 !(#^.^#)!

作者:Xin~So