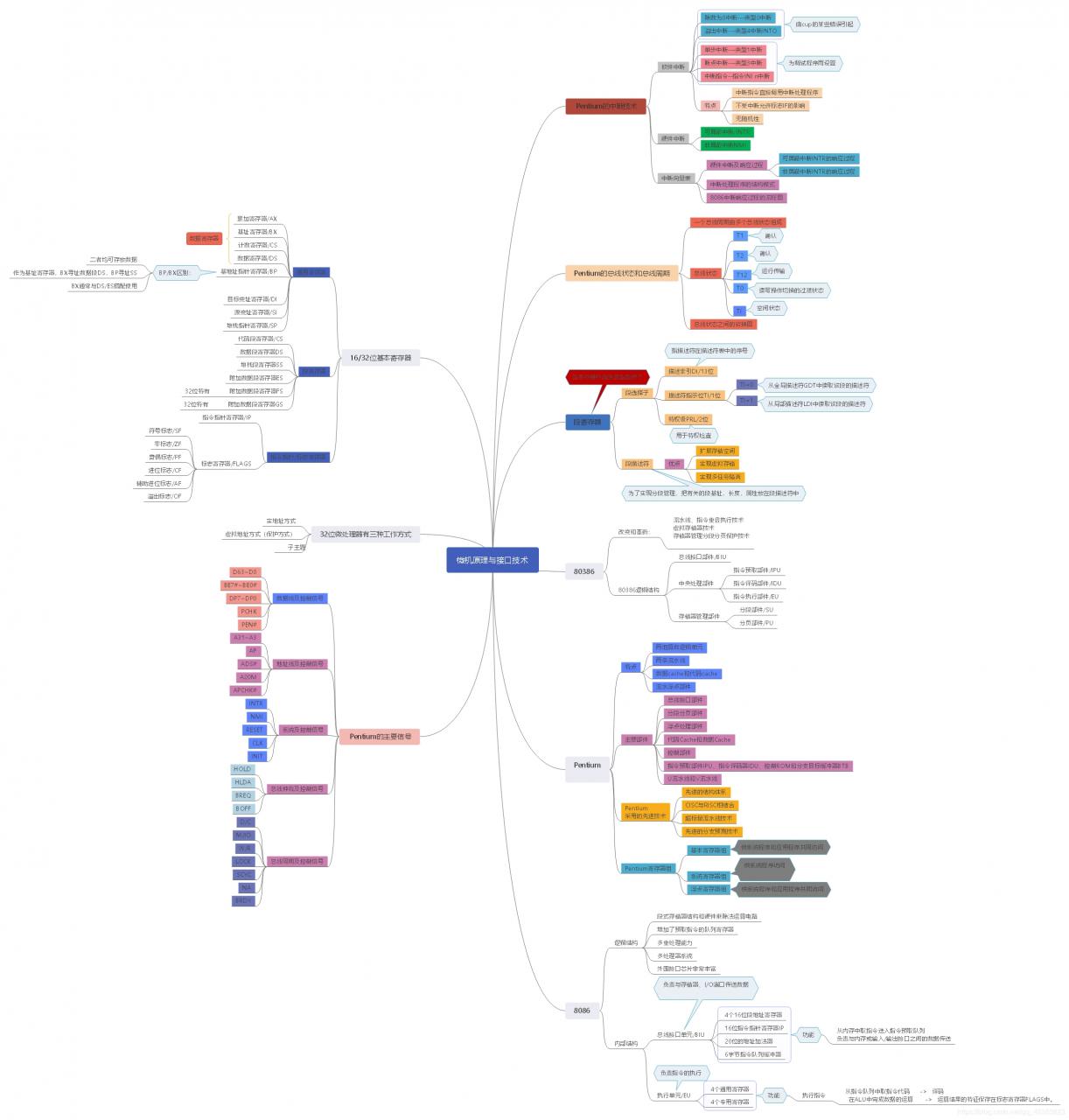

微机原理与接口技术(第二章复习必备)

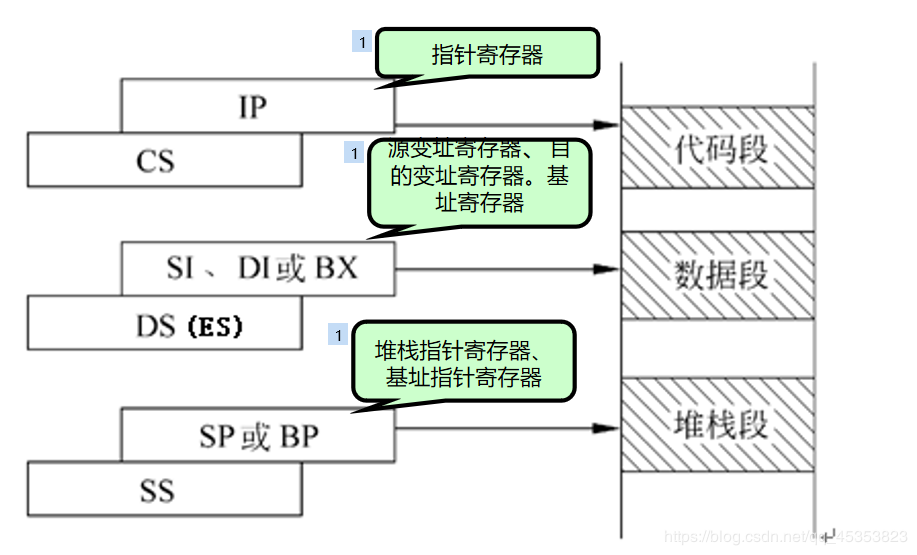

##段寄存器的使用

标志寄存器(FLAGS):用于存放系统的状态标志和控制标志。

状态标志:

是CPU在执行指令的过程中产生的。有的指令影响状态标志,

有的不影响,还有的指令与当前状态标志有关。

标志寄存器中有6个最常用,每个 占1位。分别介绍如下:

1)符号标志SF(sign flag):

它和运算结果的最高位相同。最高位为1,则为1,最高位为0,则为0。

2)零标志ZF(zero flag) :

若运算结果为0,则ZF=1;否则ZF=0。

3)奇偶标志PF(parity flag) :

若运算结果中“1”的个数为偶数,则PF=1;否则PF=0。

4)进位标志CF(carry flag) :

加法时,最高位(字节操作时的D7位,字操作时的D15位)是否有进位产生。

减法时,最高位(字节操作时的D7位,字操作时的D15位)是否有借位产生。

5)辅助进位标志AF(auxiliary flag) :

8位二进制加法时,第3位向第4位有进位。

8位二进制减法时,第3位向第4位有借位。

6)溢出标志OF(overflow flag) :

若运算过程中发生了“溢出”,则OF=1,否则OF=0。

控制标志

1)方向标志DF(direction flag)

2)中断允许标志IF(interrupt enable flag)

3)跟踪标志TF(trap flag)

1)方向标志DF(direction flag)

2)中断允许标志IF(interrupt enable flag)

3)跟踪标志TF(trap flag)

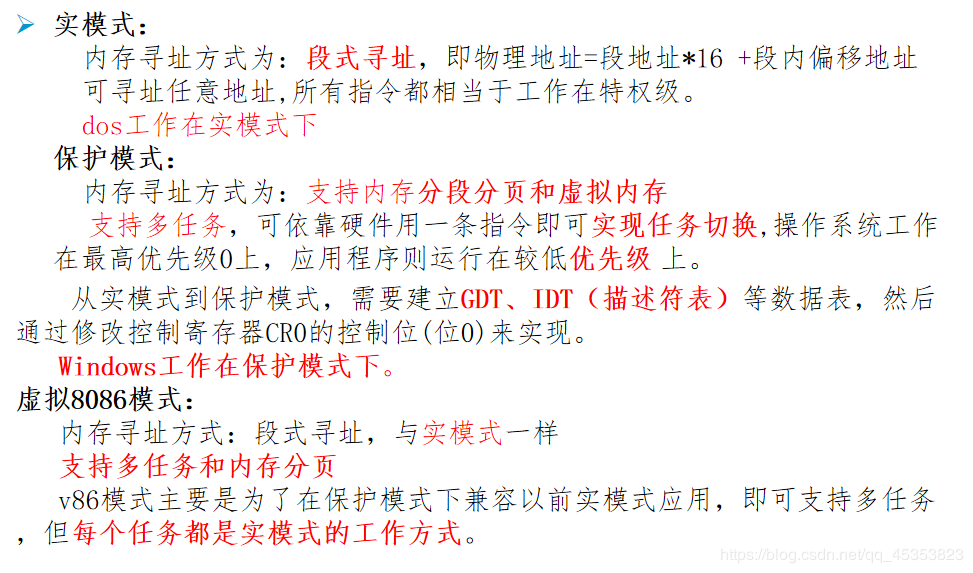

实地址模式是16位微处理器采用的方式。32微处理器位向下兼容。逻辑地址是程序员编写程序时使用的地址。实地址模式下存储单元地址为20位

1) 逻辑地址:

16位的段码和16位的偏移量组合在一起称为逻辑地址,表示方式如下:

段码:偏移量

2)物理地址:

物理地址=段首地址+偏移量=24×段码+偏移量

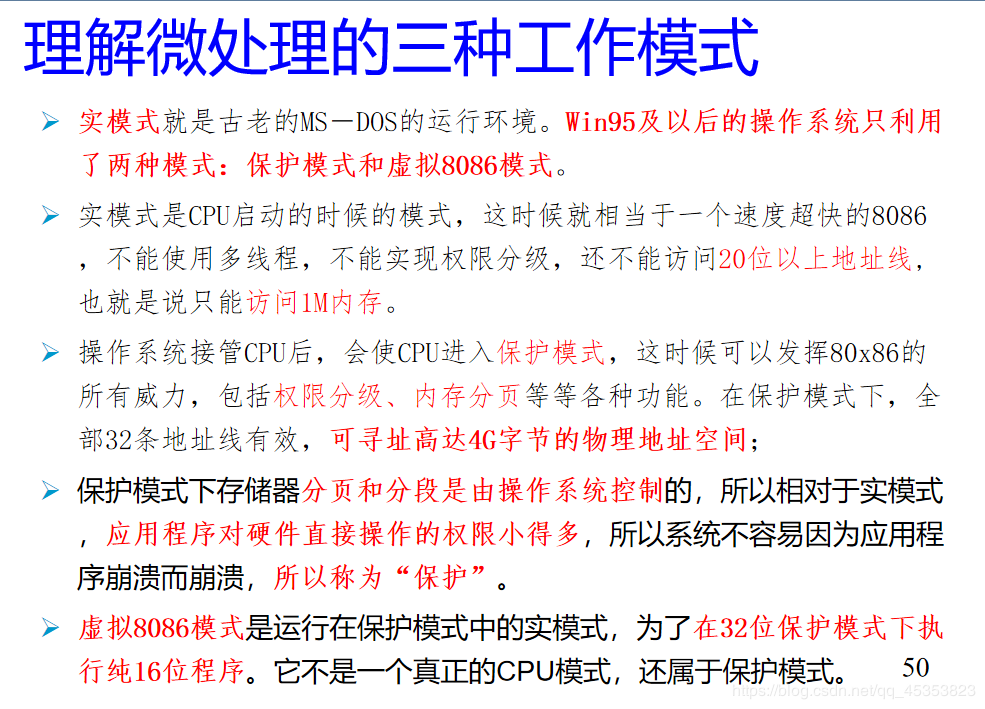

虚拟地址方式(保护方式)

是最常用的方式,适用于多任务环境,在这种方式下,

80386才能发挥它自身的 强大功能,所以也称本性方式。

它的特点是:

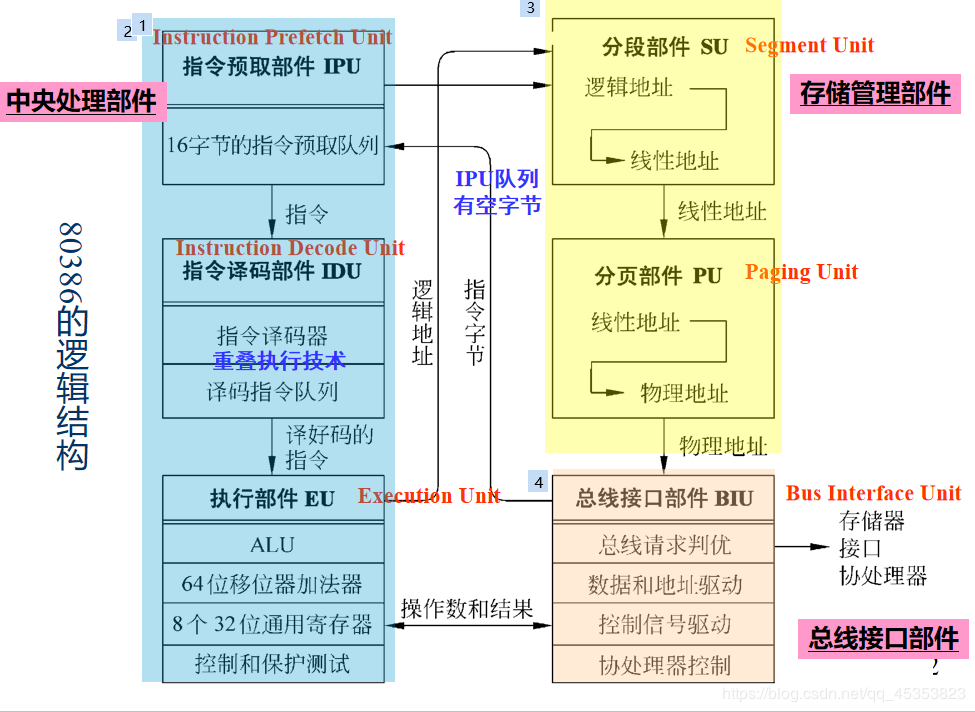

① 通过逻辑(虚拟)— 线性 — 物理地址的寻找方式来实现存储器的管理,由于 逻辑地址很大,既能实现大程序的运行,又可以方便地实现多任务的分配和管理。

② 能实现16位或32位的运算。

③ 在保护方式下,可以转入到虚拟8086的方式运行。

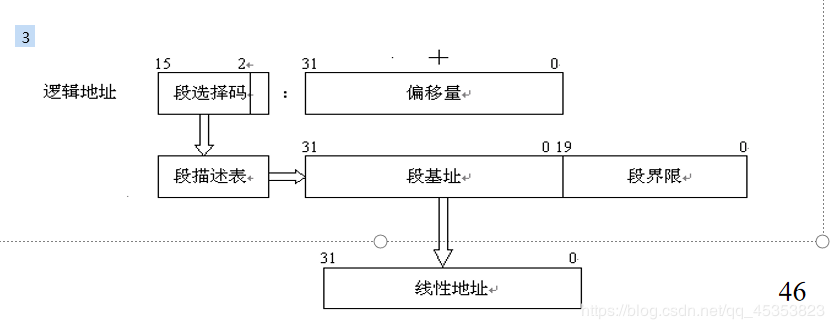

逻辑地址:

虚地址方式下,逻辑地址是由一个段选择码加上一个指定段内相对地址的偏移量,表示为 [段选择码:偏移量]。

线性地址

虚地址方式下,段基址要通过查表间接得到。段选择码的作用就是选择段描述表中的某一描述项(描述符),而在描述项中给出了32位段基址和20位的段界限(给出段的长度)。

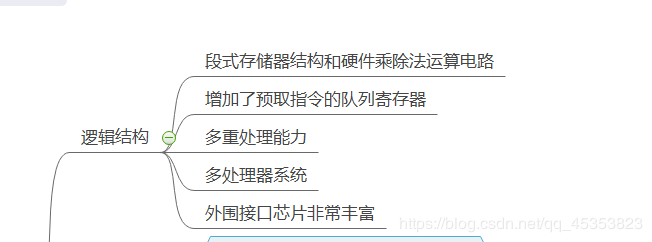

32位80386微处理器是为多用户和多任务操作系统而设计的

具有32位寄存器和数据通道

支持32位地址和数据类型

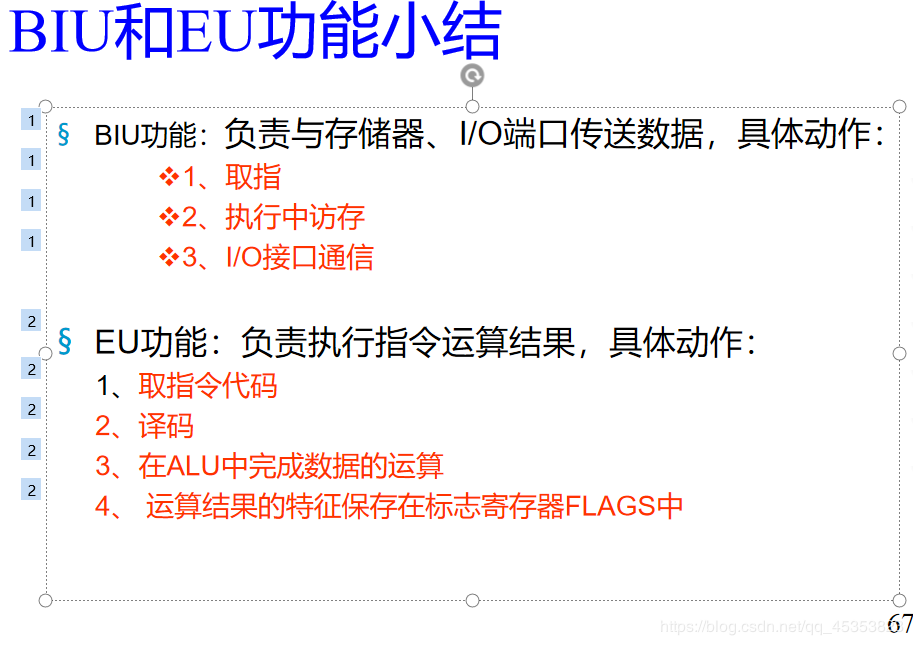

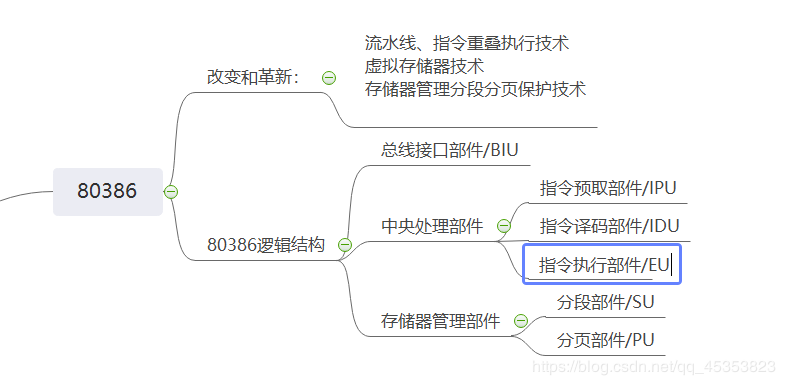

80386逻辑结构:

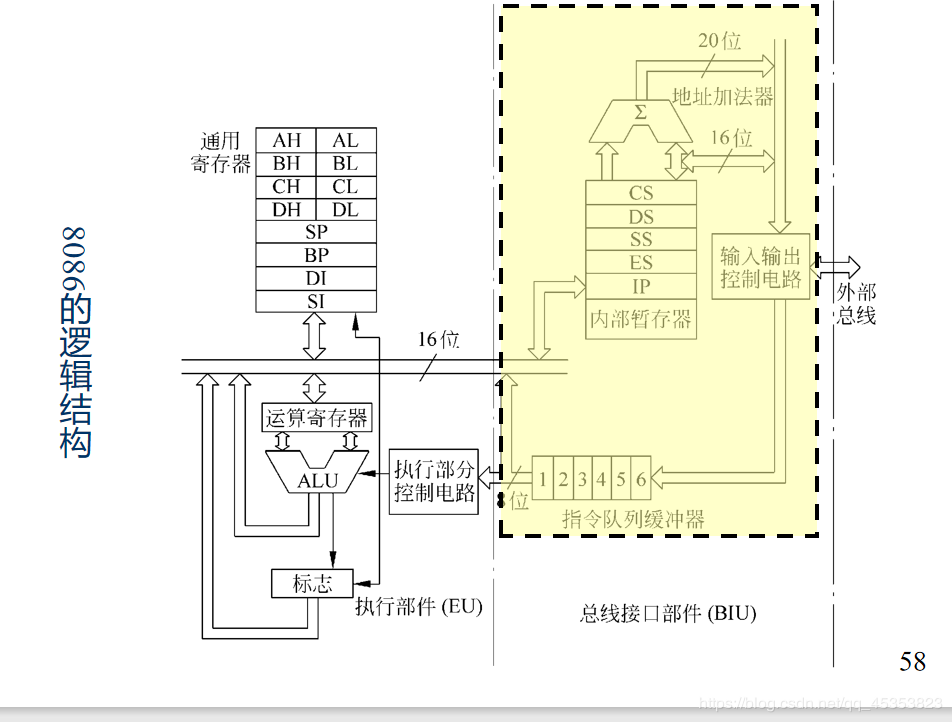

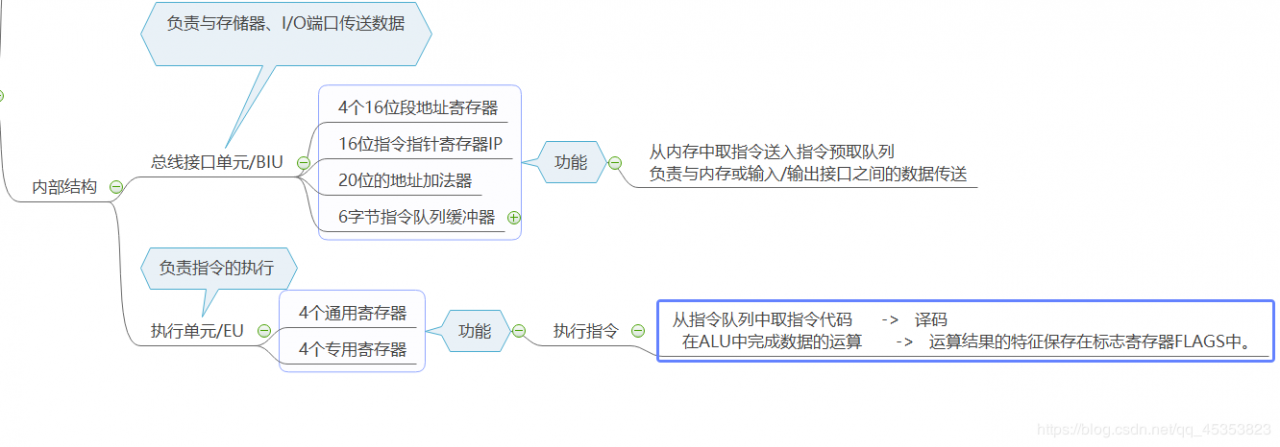

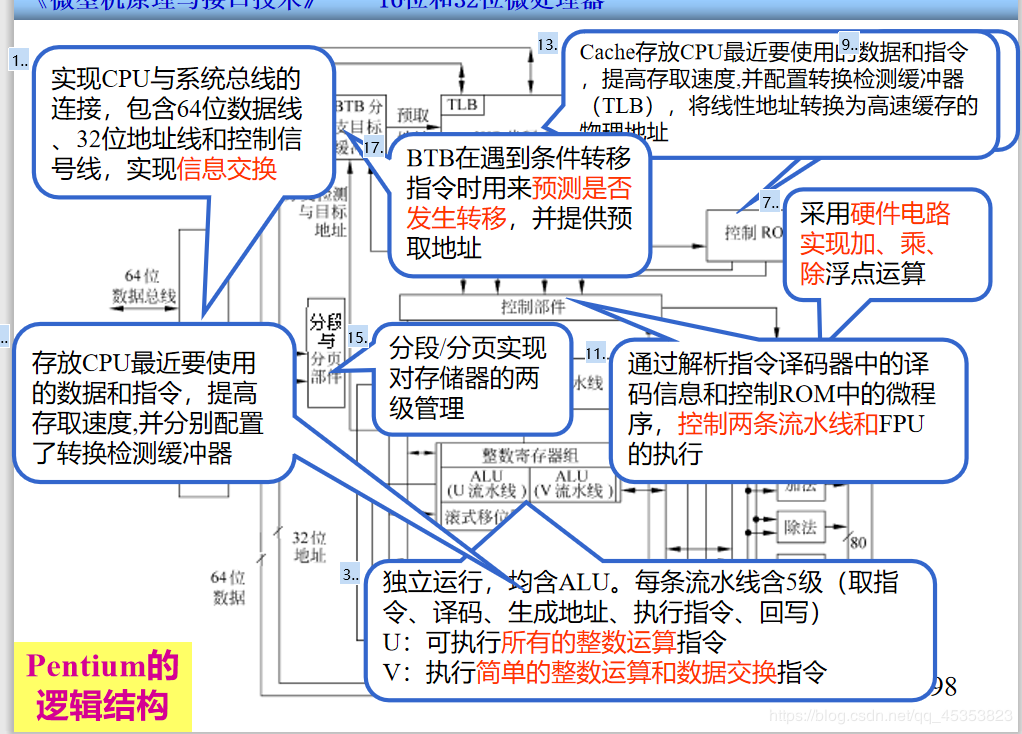

总线接口部件通过数据总线、地址总线和控制总线负责与外部取得联系,包括访问存储器预取指令,读/写数据和访问I/O端口读/写数据等全部操作及其他控制功能。

中央处理部件: 存储器管理部件MMU: 逻辑图

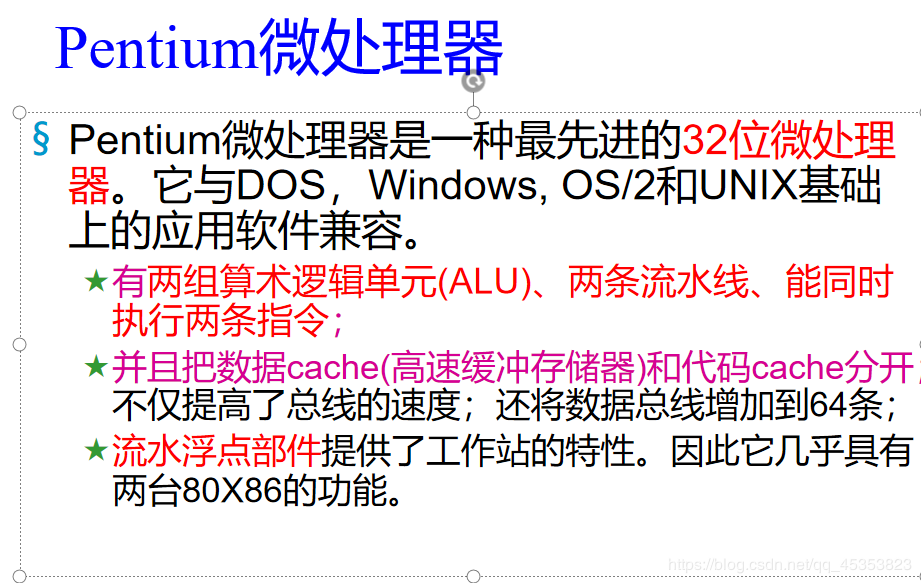

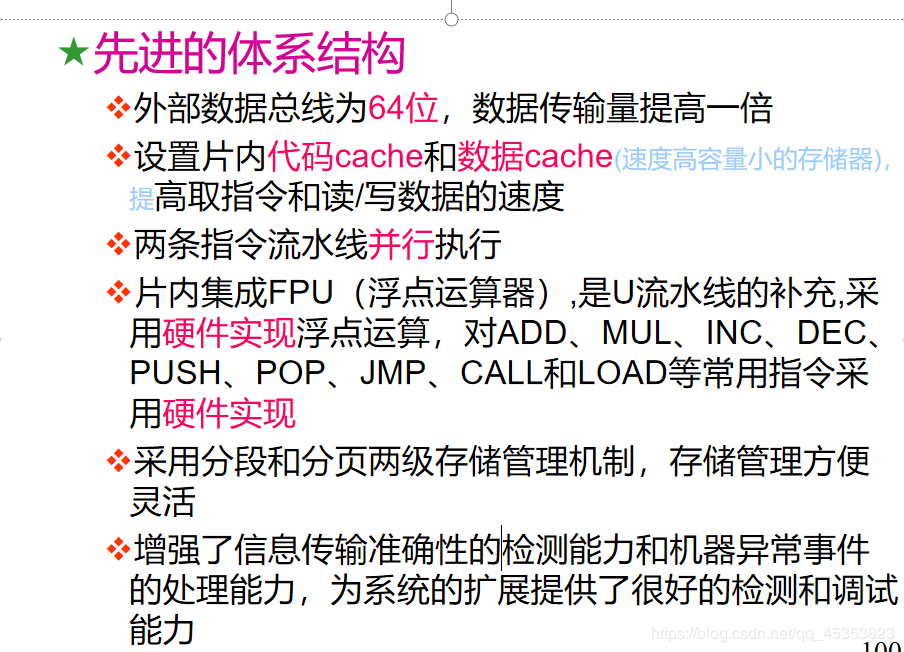

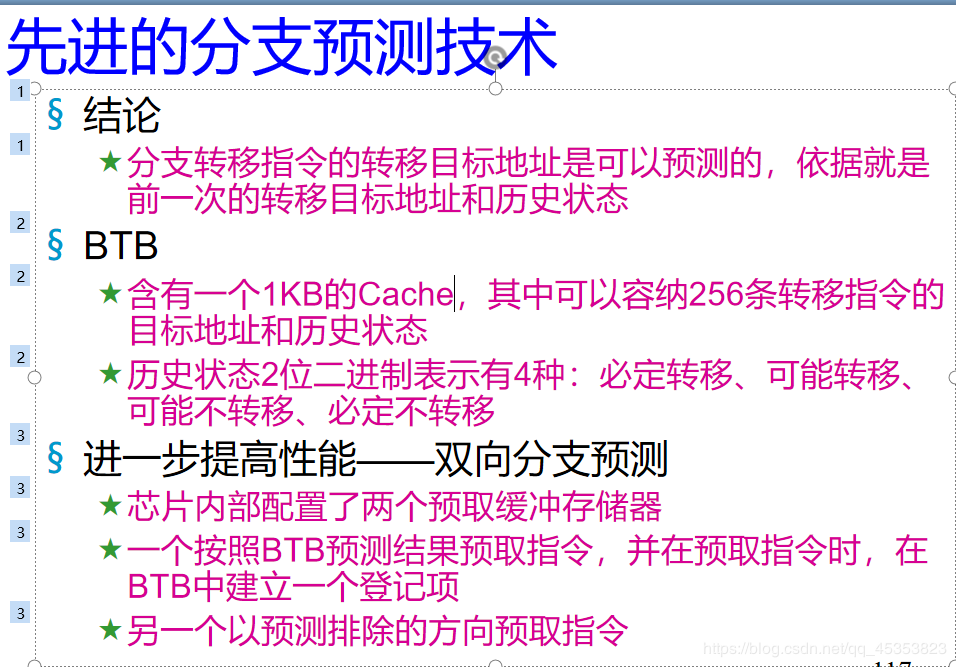

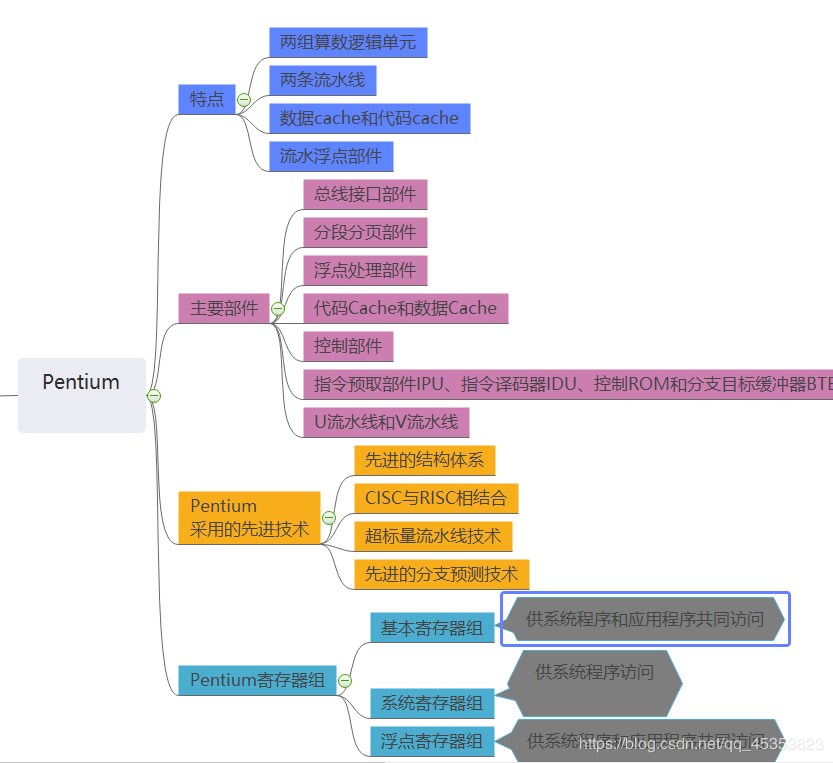

1.先进的结构体系

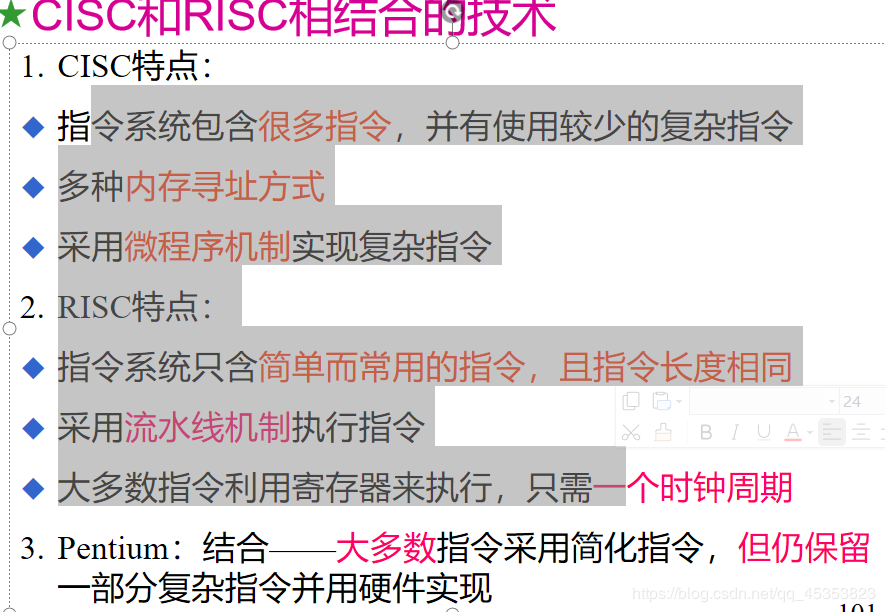

2.CISC和RISC相结合

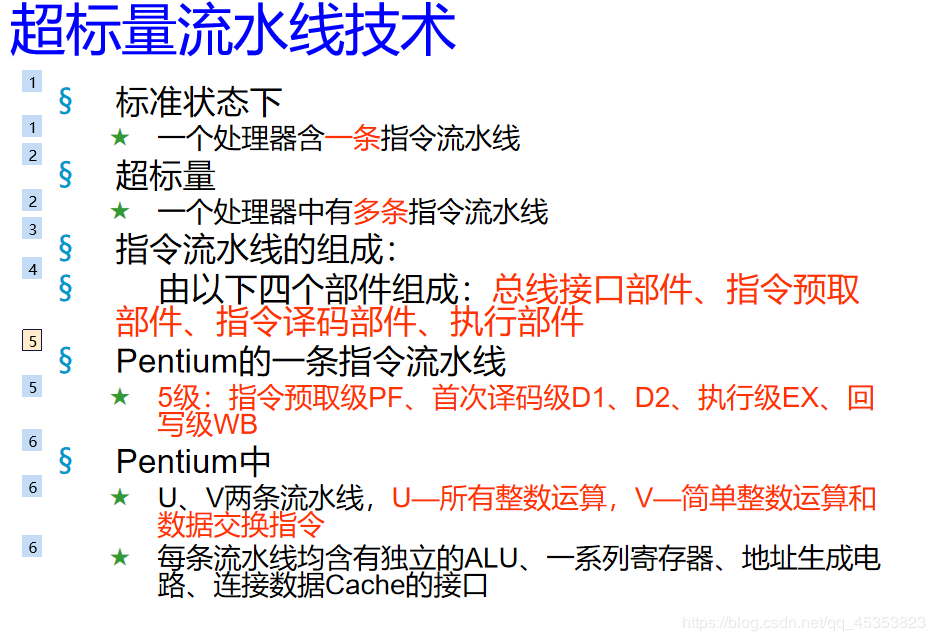

3.超标量流水线

4.先进的分支预测技术

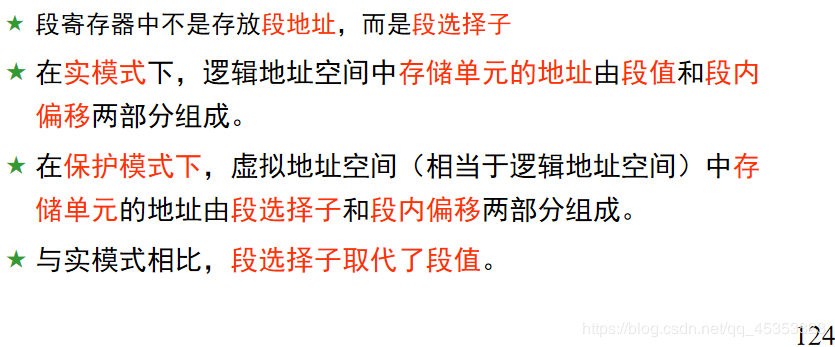

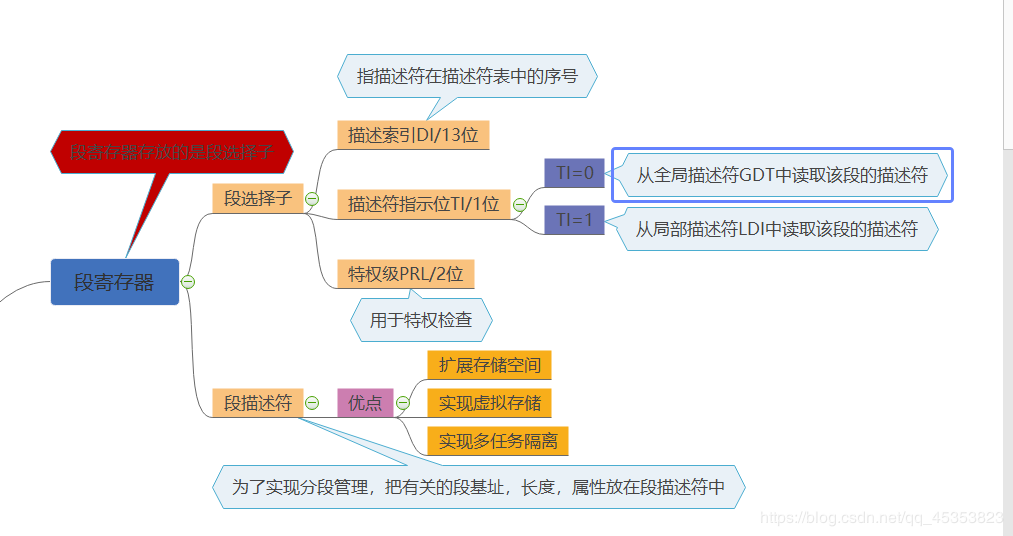

段寄存器存放的是段选择子

13+1+2(位)

13:描述索引DI:指描述符在描述符表中的序号

1:描述符指示位TI: TI=0->GDT(全局描述符)

2:**特权级PRL:**TI=1->LBI(局部描述符)

优点

扩展存储空间 实现虚拟存储 实现多任务隔离 段寄存器总结

重点了解

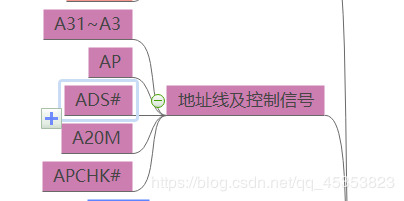

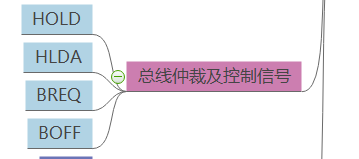

A31~A3: 地址线

AP: 地址的偶检验码位

ADS# 地址状态输出信号

A20M#:A20以上的地址线屏蔽信号

APCHK# 地址校验出错信号

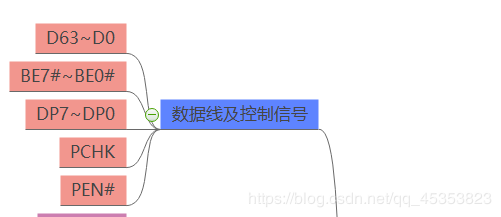

D63~D0:数据线

BE7#~BE0:字节允许信号

DP7~DP0:奇/偶校验信号

PCHK:读校验

DEN#:奇/偶校验允许信号

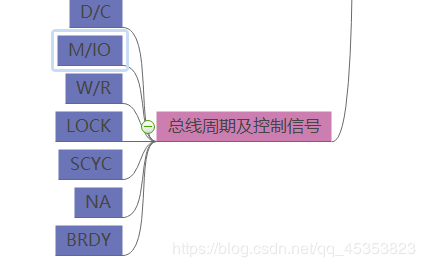

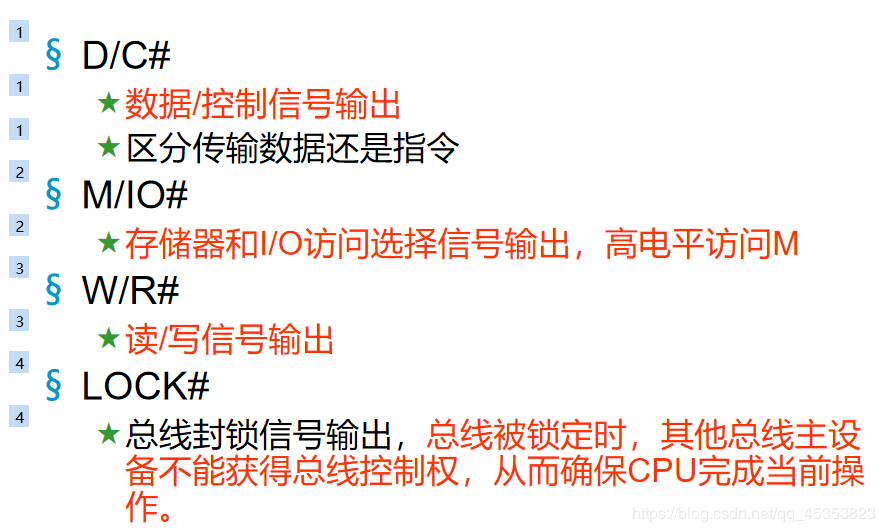

D/C:数据/控制

M/IO:存储器和IO

W/R:读/写

LOCK:总线封锁

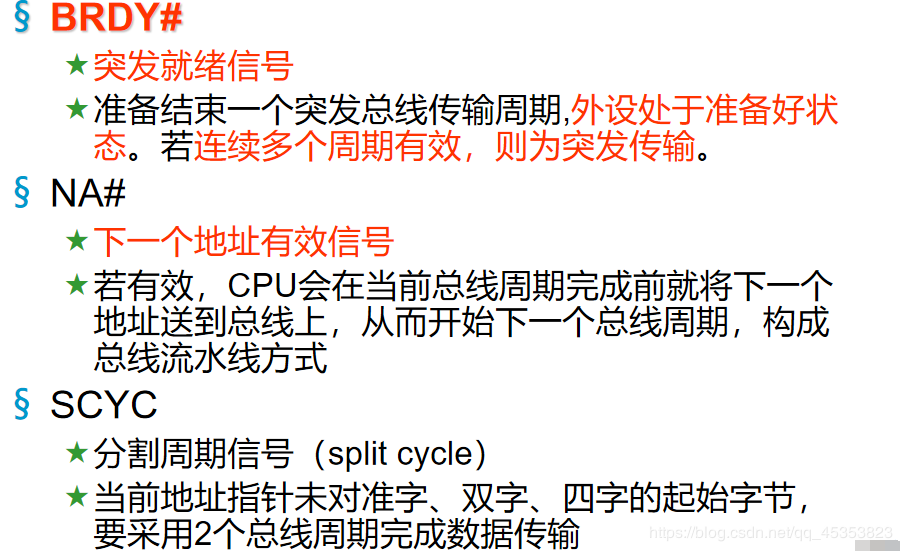

SCYC:分割周期

NA:下一个地址有效信号

BRDY:实发就绪信号

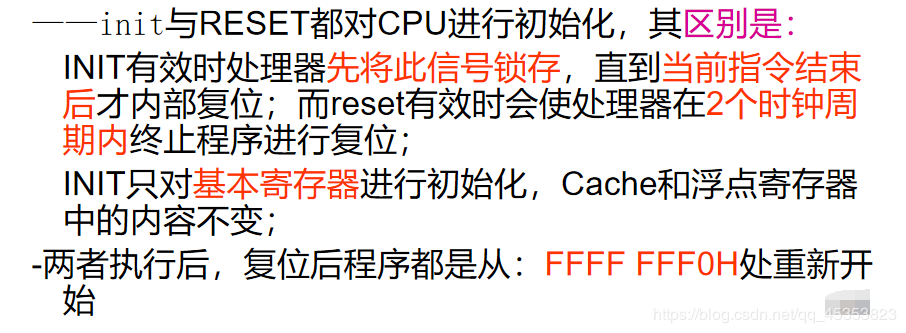

init和reset区别:

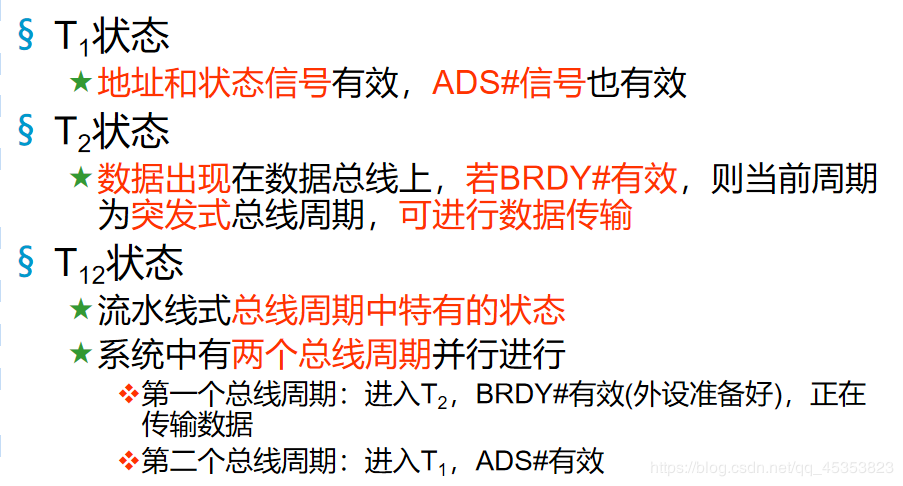

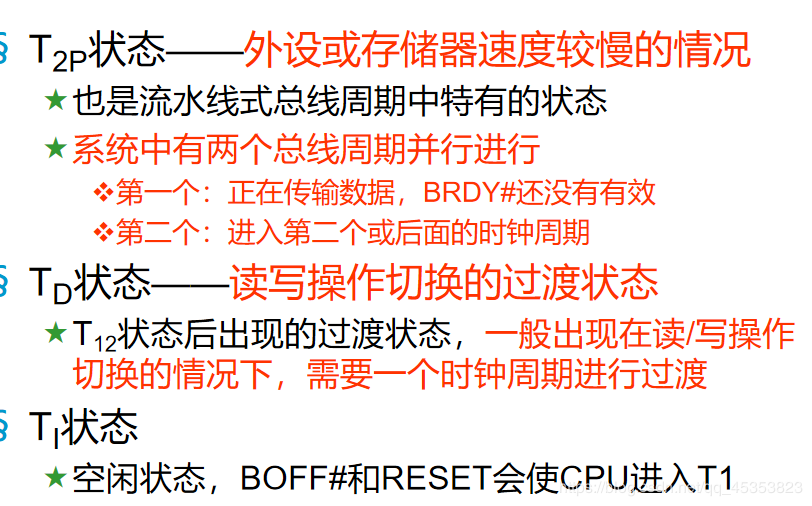

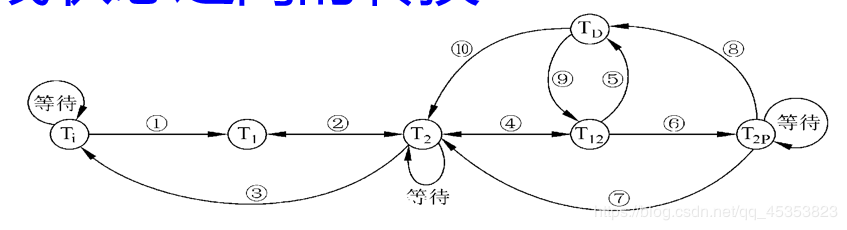

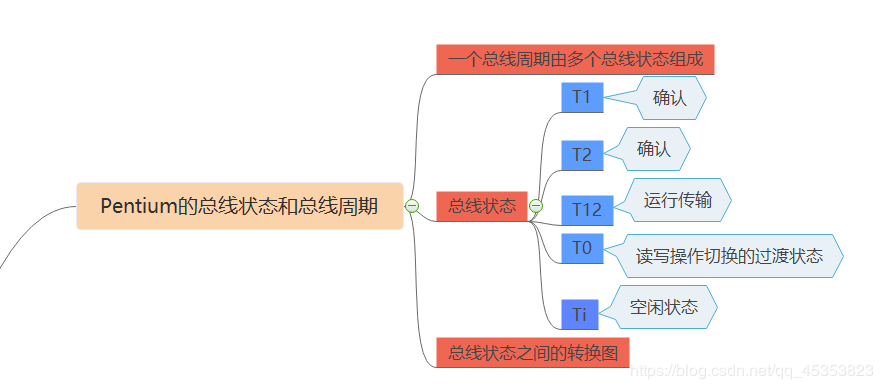

Pentium的一个总线周期通常由多个时钟周期组成,而一个时钟周期对应一个总线状态所以一个总线周期由多个总线状态组成

Pentium的几种总线状态定义

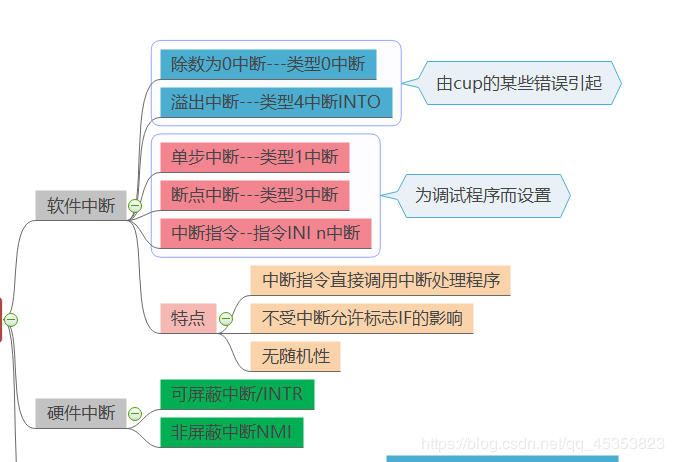

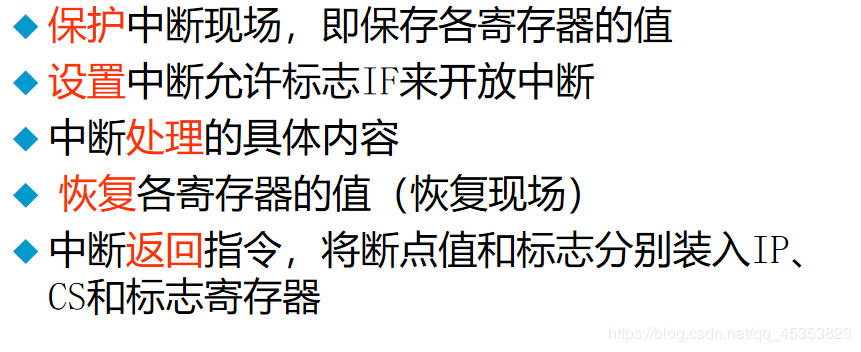

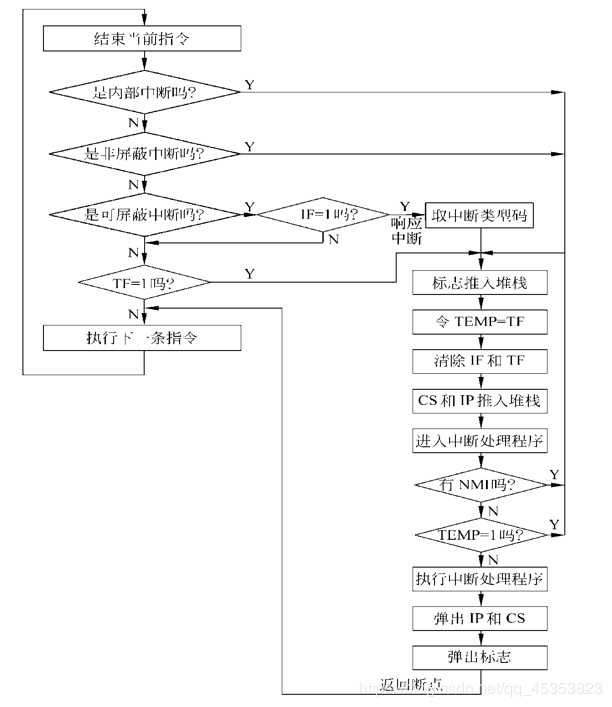

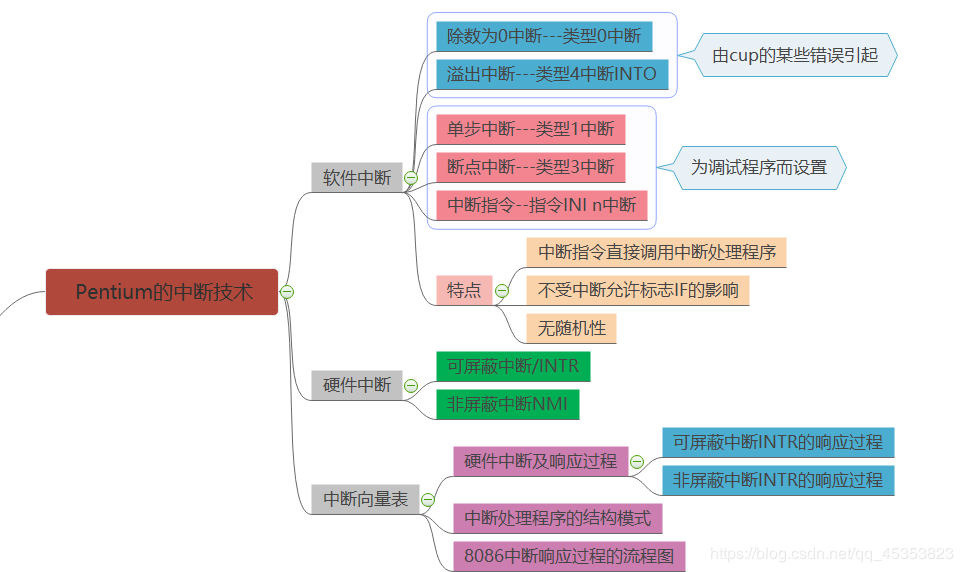

软件中断

硬件中断

概述:放置256个中断向量(入口地址)即称 中断向量表 ,每个中断矢量占据4个字节 ,地址较高的两个字节放入口地址的段地址,较低两位放置偏移地址

硬件中断以其响应过程

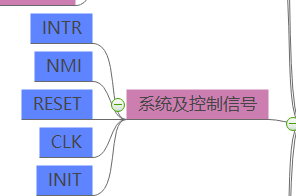

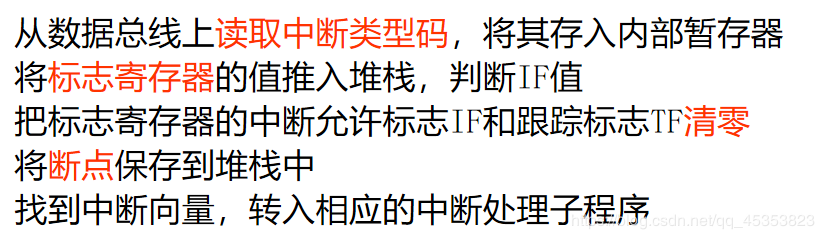

(1)可屏蔽中断INTR的响应过程

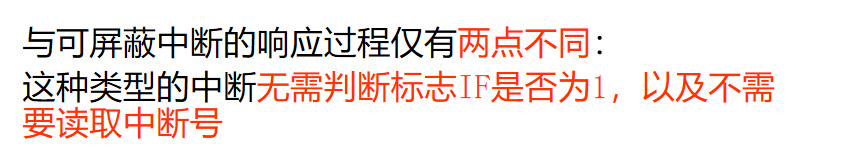

(2)非屏蔽中断INTR的响应过程

作者:至尊小涛丫