S3C2440—4.时钟系统

文章目录一.S3C2440时钟体系介绍1.总线与时钟2.时钟来源3.选择时钟4.产生时钟5.流程二.如何配置时钟源1.设置FCLK频率寄存器 MPLLCON2.设置分频HDIV、PDIV寄存器 CLKDIVN3.时钟开关控制寄存器 CLKCON

一.S3C2440时钟体系介绍

1.总线与时钟

S3C2440有俩个总线:AHB高速总线、APB外围总线。

对应三个时钟源:

ARM芯片CPU的FCLK

AHB总线的HCLK

APB总线的PCLK

三个时钟的工作频率:

(可以看出对比STM32中72MHz的频率,ARM时钟的性能有了很大的提高)

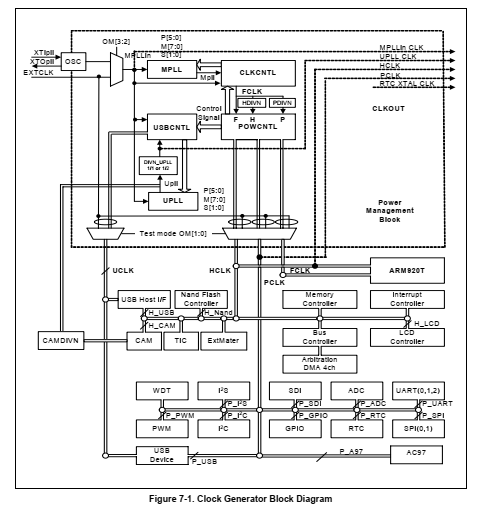

2.时钟来源如何得到三种时钟?系统的时钟来源是12MHz的晶振,通过PLL锁相环硬件设备可以得到高达400MHz的时钟频率,其时钟框图如下:

原创文章 95获赞 265访问量 5万+

关注

私信

展开阅读全文

原创文章 95获赞 265访问量 5万+

关注

私信

展开阅读全文

作者:蜡笔小新没有博客