FPGA控制LCD1602字符显示

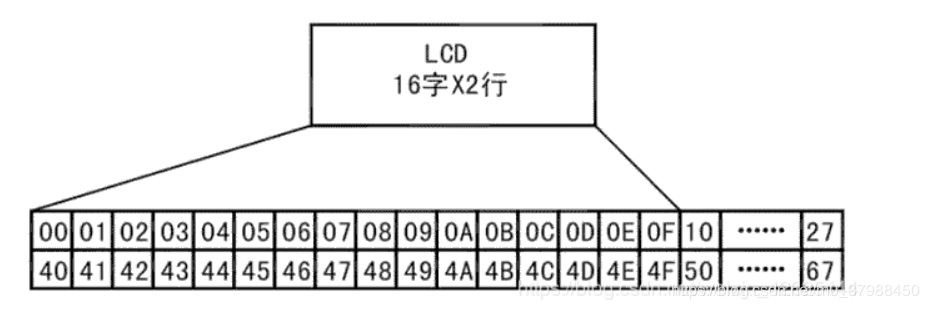

1.LCD1602(DDRAM)的外形是这样子滴:

背面:

可见区范围:16✖2行;可通过“光标或显示移动指令”使字符慢慢移动到可见的显示范围内,看到字符的移动效果。

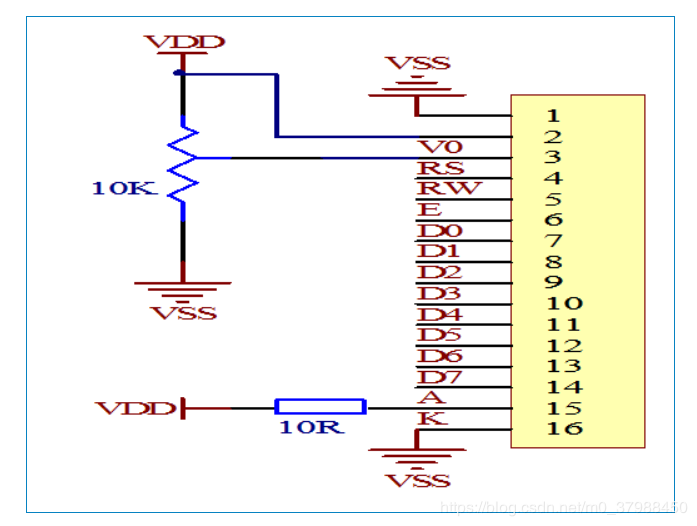

管脚分配:

2.LCD配置:

(1)通用配置

/*清屏 */

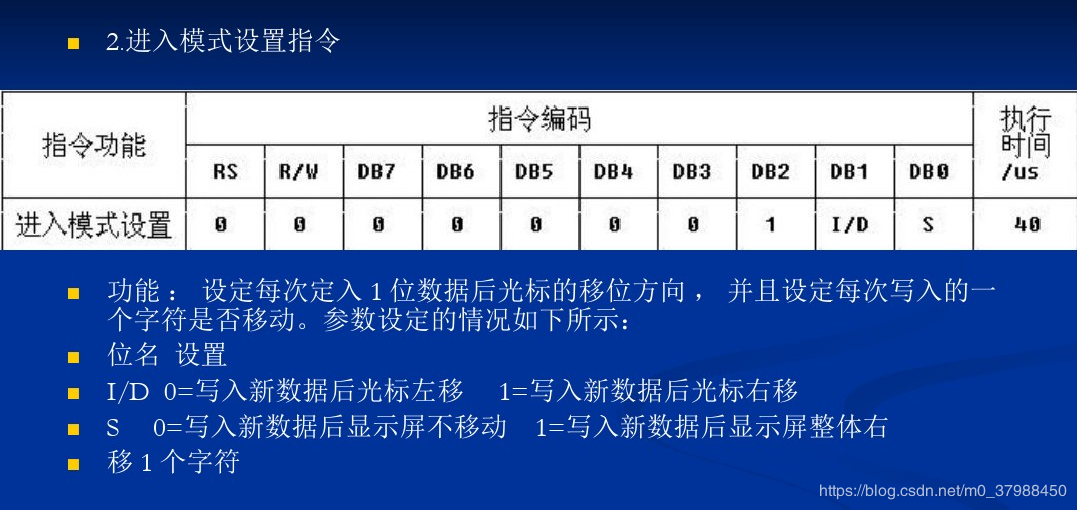

/*置输入模式 */

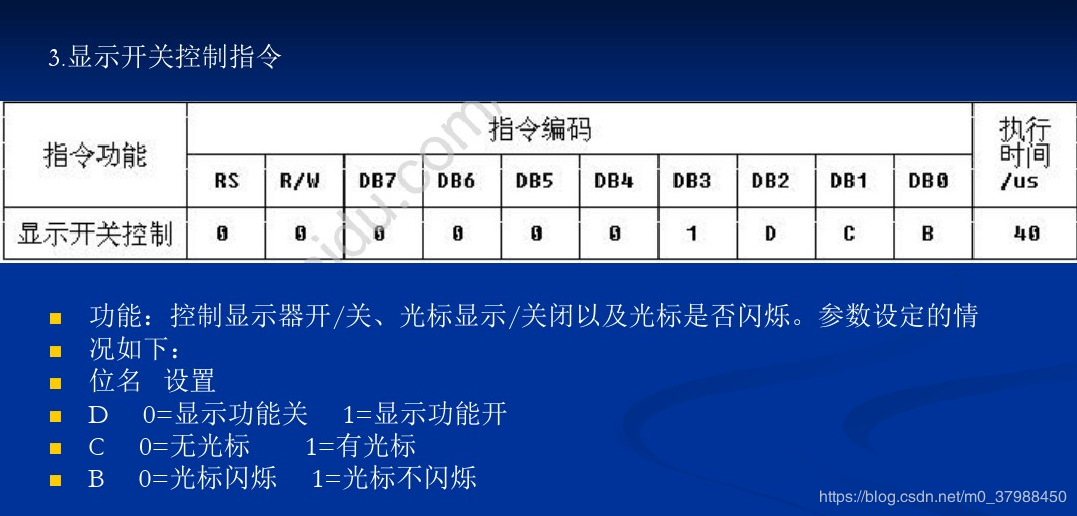

/*显示开关控制 */

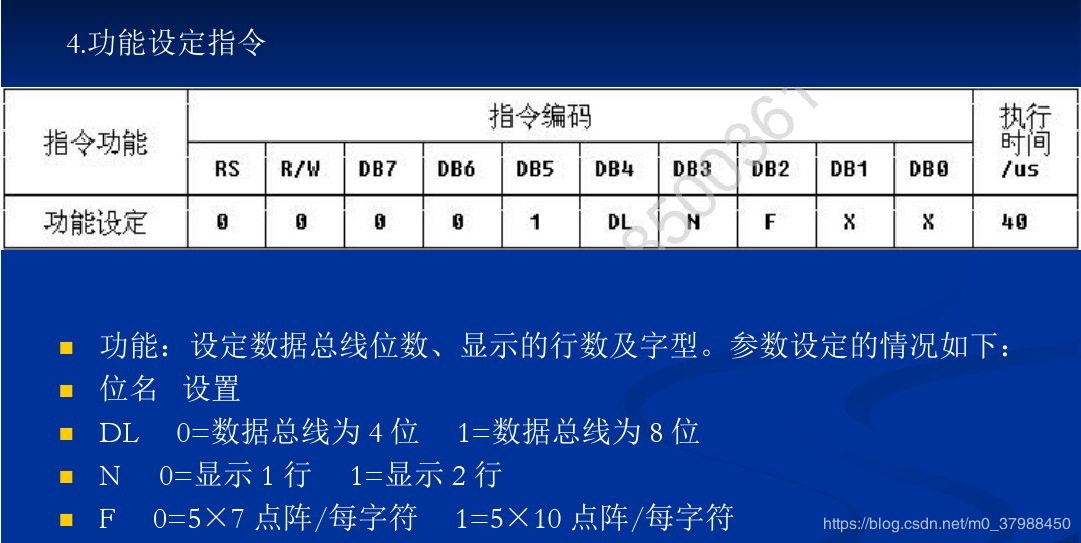

/*置功能 */

(2)显示数据

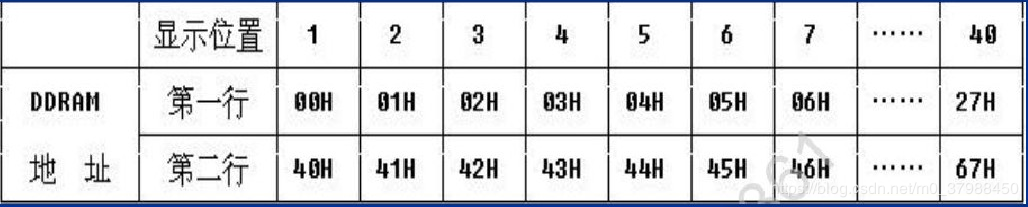

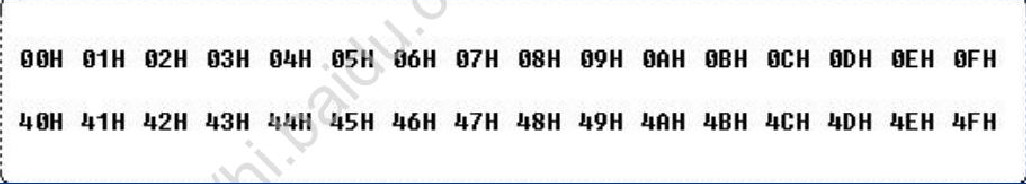

只配置前16个地址(如下),用于显示:

之后逐次配置第一行、第二行的地址和数据:

/*置第一行地址 */

/*置第一行数据 */

/*置第二行地址 */

/*置第二行数据 */

3.FPGA实现:

module LCD1602(

input clk,

input rst_n,

output reg RS,

output reg RW,

output reg E,

output reg [7:0]DB

);

reg [30:0]counter;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

counter<=0;

E<=0;

end

else

begin

if(counter<24999)

counter<=counter+1;

else

begin

counter<=0;

E<=~E;

end

end

end

reg [3:0]state;

reg [127:0]disp_data1;

reg [47:0]disp_data2;

reg [3:0]cnt;

always@(posedge E or negedge rst_n)

begin

if(!rst_n)

begin

state<=0;

RS<=0;

RW<=0;

DB<=0;

disp_data1<="welcome you come";

disp_data2<="123456";

end

else

begin

case(state)

0:begin

RS<=0;

RW<=0;

DB<=8'b00111000;

state<=1;

end

1:begin

RS<=0;

RW<=0;

DB<=8'b00001100;

state<=2;

end

2:begin

RS<=0;

RW<=0;

DB<=8'b00000001;

state<=3;

end

3:begin

RS<=0;

RW<=0;

DB<=8'b00010100;

state<=4;

end

4:begin

RS<=0;

RW<=0;

DB<=8'b10000000;

state<=5;

end

5:begin

RS<=1;

RW<=0;

DB<=disp_data1[127:120];

disp_data1<={disp_data1[119:0],disp_data1[127:120]};

cnt<=cnt+1;

if(cnt==15)

begin

state<=6;

cnt<=0;

end

end

6:begin

RS<=0;

RW<=0;

DB<=8'b11000101;

state<=7;

end

7:begin

RS<=1;

RW<=0;

DB<=disp_data2[47:40];

disp_data2<={disp_data2[39:0],disp_data2[47:40]};

cnt<=cnt+1;

if(cnt==5)

begin

state<=4;

cnt<=0;

end

end

default:;

endcase

end

end

endmodule

作者:不秃就一直搞

相关文章

Zarah

2021-02-22

Winema

2020-10-19

Kathy

2023-07-19

Nora

2023-07-19

Serafina

2023-07-20

Mathilda

2023-07-20

Aggie

2023-07-20

Fawziya

2023-07-20

Catherine

2023-07-20

Ebony

2023-07-20

Lark

2023-07-20

Olive

2023-07-20

Phemia

2023-07-20

Viridis

2023-07-20

Hazel

2023-07-20

Serafina

2023-07-21

Kitty

2023-07-21

Serwa

2023-07-21

Catherine

2023-07-21