FPGA 处理视频SDRAM带宽计算(四画面视频分割器 4K@30输出)

FPGA 处理视频SDRAM带宽计算(四画面视频分割器 4K@30输出)

FPGA 四画面视频分割器SDRAM的带宽计算

作者:qq_708907433

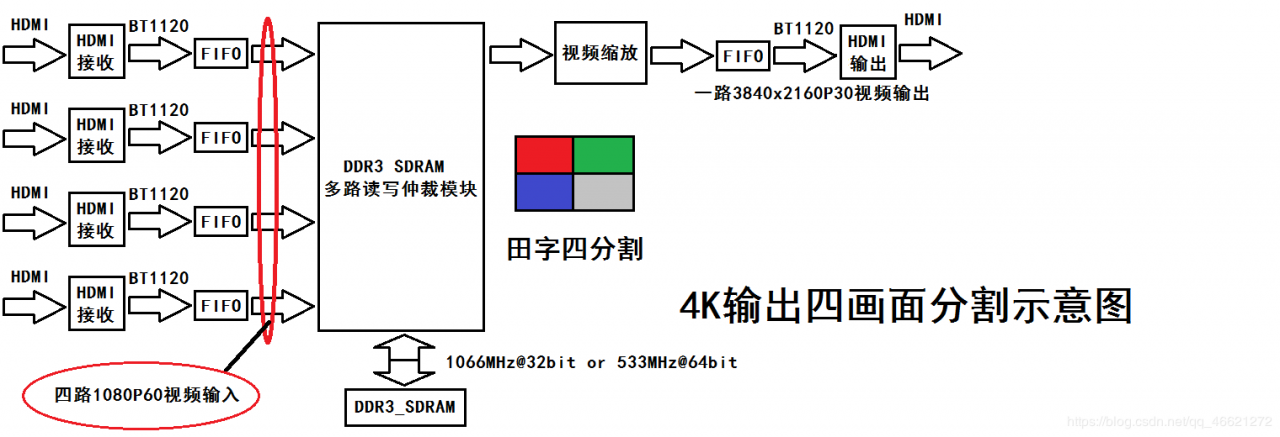

4K 四画面分割器,将四路1080P60视频分割在一个屏上输出3840x2160P30。

按2x2 田字四画面分割器举例,见下图,四路1080P60视频进内存,一路4K30视频出内存送显示屏。

四路视频进内,一路视频出内存。

这个方案需要占用

1920x1080x60x4/0.8 + 3840x2160x30x1/0.8= 933MHz@32 带宽。

做这个产品硬件设计时需要选大于 1066MHZ@32bit 或 533MHZ@64bit 内存方案 (DDR/DDR2/DDR3/DDR4)

该方案中1080P视频不放大,直接进内存。见下图。

由于分割输出的分辨率4K 比输入 2K 大,在实际使用中不少用户希望能将2K输入放大后在4K中分割输出。

用户的额外要求看似简单,实际实现起来非常麻烦,对FPGA 及DDR3 SDRAM带宽的占用需要重新考虑。由于输入的视频需要放大,而视频放大只能在视频出DDR3 SDRAM 之后(具体原因见FPGA 视频处理中外部SDRAM的作用)

这4路输入的视频实际进出DDR3 SDRAM 2次,具体实现与四画面拼接单元的逻辑图接近。这里就不再专门阐述。

FPGA 多屏多画面视频拼接器

采用FPGA构建数字视频矩阵的一些设计思路和设计需求

FPGA 四画面视频分割逻辑框图

FPGA 四画面视频拼接单元逻辑框图

FPGA 视频处理中外部SDRAM的作用

FPGA 处理视频SDRAM带宽计算

FPGA 处理视频SDRAM带宽计算(四画面视频分割器)

FPGA 处理视频SDRAM带宽计算(四画面视频分割器 4K@30输出)

作者:qq_708907433

相关文章

Nabila

2021-07-22

Zarah

2021-02-22

Sophia

2020-12-28

Julie

2021-06-19

Maha

2023-02-26

Kathy

2023-02-26

Haidee

2023-03-17

Tani

2023-04-08

Kathy

2023-04-24

Miette

2023-05-12

Serena

2023-05-12

Elizabeth

2023-05-12

Valora

2023-05-12

Hana

2023-05-12

Ursula

2023-05-12

Ula

2023-05-17

Fawn

2023-07-17

Bea

2023-07-20

Irma

2023-07-20