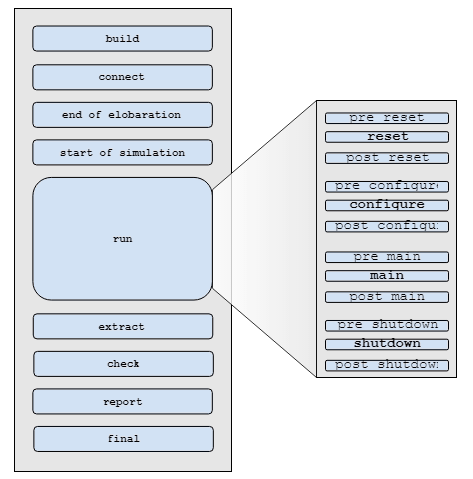

[SV]UVM Phases top down

The run phase is implemented as a task and remaining all are function.

Phases can be grouped into 3 categories,

1. Build Phases build phase, connect phase and end_of_elobaration phase belongs to this category.Phases in this categorize are executed at the start of the UVM testbench simulation, where the testbench components are constructed, configured and testbench components are connected.All the build phase methods are functions and therefore execute in zero simulation time.

start of simulation and run phase belongs to run-time phases, the run phase will get executed from the start of simulation to till the end of the simulation.the run phase is time-consuming, where the testcase is running

3. Clean up Phasesextract, check, report and final belong to this category.where the results of the testcase are collected and reported. example: the number of error’s during the simulation is reported.

二、Phases Description:| Phase | Description | Execution Order |

|---|---|---|

| build | Used to construct the testbenchcomponents | top-down |

| connect | Used to connect TLM ports of components | bottom-up |

| end_of_elaboration | Used to make any final adjustments to the structure, configuration or connectivity of the testbench before simulation starts | bottom-up |

| start_of_simulation | used for printing testbench topology or configuration information | bottom-up |

| run | Used for stimulus generation, driving, monitoring, and checking | parallel |

| extract | Used to retrieve and process information from scoreboards and functional coverage monitors | |

| check | Used to check that the DUT behaved correctly and to identify any errors that may have occurred during the execution of the test bench | |

| report | Used to display the results of the simulation or to write the results to file | |

| final | Used to complete any other outstanding actions that the test bench has not already completed |

the run phase has different phases, these are,

| run | Phase | Description |

|---|---|---|

| pre_reset | the pre_reset phase starts at the same time as the run phase. Its purpose is to take care of any activity that should occur before the reset, such as waiting for a power-good signal to go active | |

| reset | The reset phase is reserved for DUT or interface specific reset behavior. For example, this phase would be used to generate a reset and to put an interface into its default state | |

| post_reset | Intended for any activity required immediately the following reset | |

| pre_configure | pre_configure phase is intended for anything that is required to prepare for the DUT’s configuration process after reset is completed | |

| configure | configure phase is used to program the DUT and any memories in the testbench so that it is ready for the start of the test case | |

| post_configure | post_configure phase is used to wait for the effects of configuration to propagate through the DUT, or for it to reach a state where it is ready to start the main test stimulus | |

| pre_main | pre_main phase is used to ensure that all required components are ready to start generating stimulus | |

| main | This is where the stimulus specified by the test case is generated and applied to the DUT. It completes when either all stimulus is exhausted or a timeout occurs | |

| post_main | This phase is used to take care of any finalization of the main phase | |

| pre_shutdown | This phase is a buffer for any DUT stimulus that needs to take place before the shutdown phase | |

| shutdown | The shutdown phase is used to ensure that the effects of the stimulus generated during the main phase have propagated through the DUT and that any resultant data has drained away | |

| post_shutdown | Perform any final activities before exiting the active simulation phases. At the end of the post_shutdown phase, the UVM testbench The execution process starts the cleanup phases |

作者:gsithxy