FPGA 处理视频SDRAM带宽计算(四画面拼接单元)

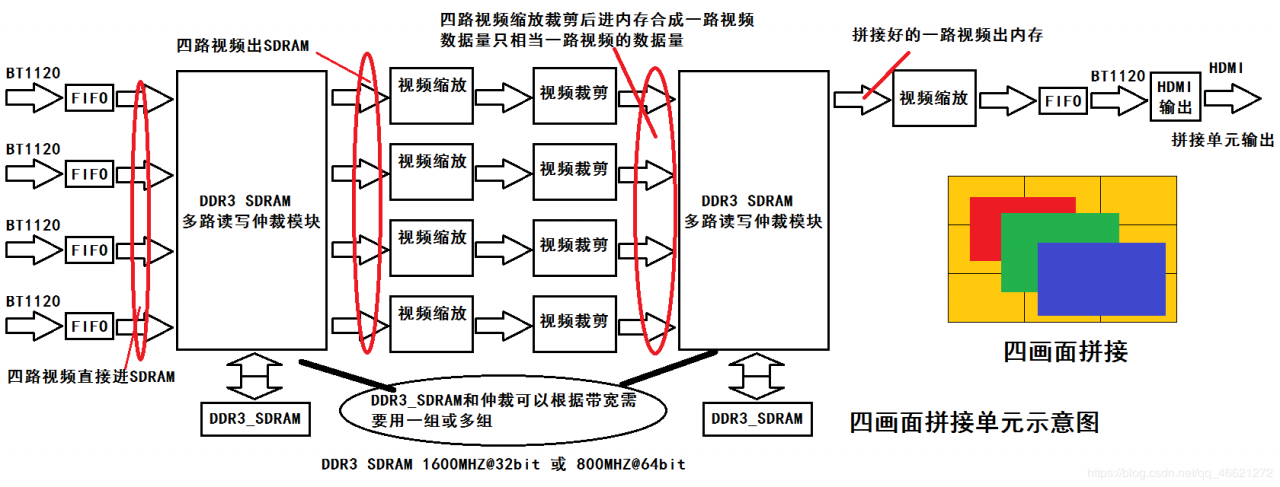

与分割相比,由于拼接需要实现每路输入视频的放大/缩小,由于视频放大只能在出 DDR3 SDRAM 之后(具体原因见FPGA 视频处理中外部SDRAM的作用)。

所以拼接单元比分割器更复杂一些。

实现拼接器主要有以下几种思路,各有优缺点,欢迎行家们参与讨论。

1:土豪金,多路输入视频不裁剪直接进出内存,独立计算带宽。硬件成本高,功耗大。FPGA 代码思路清晰简单,容易实现,毛病BUG会很少。

1920x1080x60x4/0.8 + 1920x1080x60x4/0.8 + 1920x1080x60x1/0.8 + 1920x1080x60x1/0.8 = 1555MHz@32 带宽。

(四路视频裁剪进SDRAM)(四路视频裁剪出SDRAM)(四路视频缩放后再进) (一路路视频输出)

按这个思路,产品硬件设计时需要选大于 1600MHZ@32bit 或 800MHZ@64bit 内存方案 (DDR/DDR2/DDR3/DDR4)

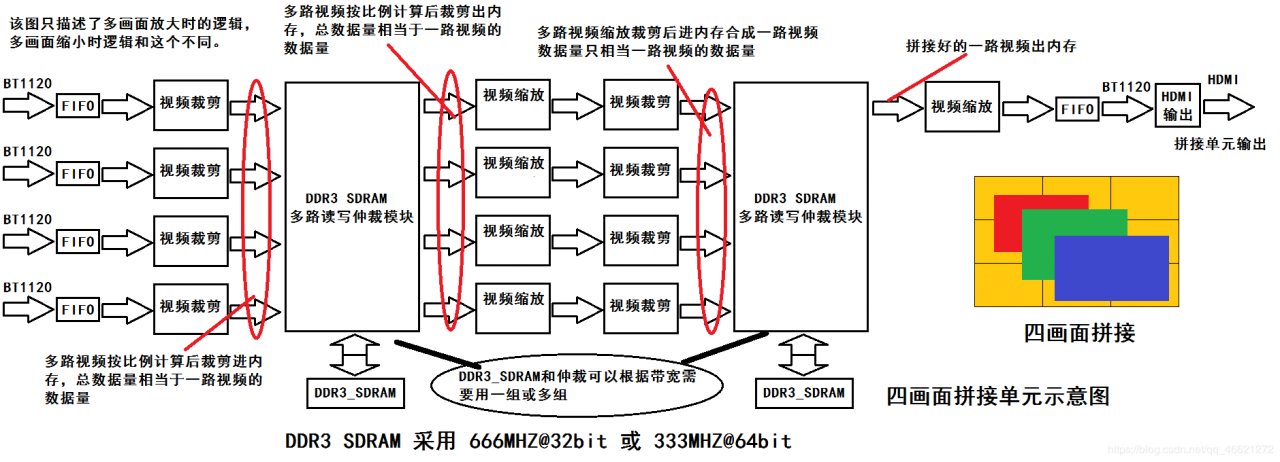

2:脑白金,多路输入视频裁剪后进出内存(SDRAM 视频写裁剪,SDRAM 视频读裁剪),复合计算带宽。硬件成低,功耗小。FPGA 代码思路比较复杂,不容易实现,调试麻烦BUG会很多。

(SDRAM 视频读裁剪,只将一个矩形视频中有用的未被遮挡裁剪的视频读出。比如只读出“凹”字形状视频数据,会减少很多的SDRAM带宽。)

按这样的思路计算,多路视频裁剪进出SDRAM,只相当于一路视频进出SDRAM的数据量。再计算缩放后进入SDRAM拼接输出。结果如下

1920x1080x60x1/0.8 + 1920x1080x60x1/0.8 + 1920x1080x60x1/0.8 + 1920x1080x60x1/0.8 = 622MHz@32 带宽。

(多路视频裁剪进SDRAM)(多路视频裁剪出SDRAM)(多路视频缩放后再进) (一路路视频输出)

按这个思路,产品硬件设计时需要选大于 666MHZ@32bit 或 333MHZ@64bit 内存方案 (DDR/DDR2/DDR3/DDR4)

和上个方案比对,带宽省太多了,能实现多路远比四路多。

FPGA 多屏多画面视频拼接器

采用FPGA构建数字视频矩阵的一些设计思路和设计需求

FPGA 四画面视频分割逻辑框图

FPGA 四画面视频拼接单元逻辑框图

FPGA 视频处理中外部SDRAM的作用

FPGA 处理视频SDRAM带宽计算

FPGA 处理视频SDRAM带宽计算(四画面视频分割器)

FPGA 处理视频SDRAM带宽计算(四画面视频分割器 4K@30输出)

FPGA 处理视频SDRAM带宽计算(四画面拼接单元)

作者:qq_708907433